本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

随着集成电路设计复杂度的提高和产品上市时间压力的增大,基于IP 核复用的SoC 设计已成为一种重要的设计方法。

在SoC 中集成的IP 核越来越多时,IP 核的互连策略和方法就成为了影响SoC 性能、数据吞吐率等指标的重要因素。本文除了介绍目前流行的总线互连策略,还介绍了正在兴起的片上网络NoC(Network-on-Chip)方法。

1、 引言

半导体加工工艺的不断进步和市场对集成电路产品的需求推动了集成电路设计技术的发展。ASIC 技术作为一种重要的IC 设计方法,主要适用于量大使用周期较长的IC 产品,一款ASIC 芯片,其开发周期大致在1 年左右。对于要实现多功能配置、更新换代很快的IC 产品,ASIC 设计方法很难满足要求。以IP 核复用为基础的SoC 设计方法,以其快速的产品上市时间、良好的功能可配置性日益成为IC 设计的重要方法。先进的加工工艺也为SoC 芯片的制造实现提供了制程支持。

在SoC设计中,一个重要的课题就是IP核的互连问题,即当一个SoC中需集成几十个,甚至更多的IP核时,如此多的IP核以怎样的方式进行数据交互。

IP核互连的不同形式会影响到SoC芯片的数据带宽、时延、数据吞吐率及功耗等指标。 总线是目前SoC设计中广为使用的IP核互连方式,常用的总线ARM 的AMBA(Advanced Microcontroller Bus Architecture) 总线、IBM 的CoreConnect总线、Silicore 公司的Wishbone总线、Altera 的Avalon总线、PlamchIP 的CoreFrame总线、MIPS 的EC Interface总线、Altera 的Atlantic? Interface总线、IDT 的IPBus(IDT Peripheral Bus) 总线等。当SoC变得越来越复杂时,总线也逐渐成为限制芯片速度、功耗、面积、数据吞吐率的一个瓶颈问题。在总线的发展中,增加总线的宽度、提高总线的时钟、支持流水线、采用多路选择器替换三态门及采用多总线方案等都可以一定程度的缓解以上问题。

然而,总线架构的不断发展与进步却给IP核复用及SoC设计实现带来了一定的不利影响。一方面,总线的技术变更或升级有可能使以前支持的IP核不再适用,需要做修改;另一方面,可能会给SoC的系统级设计带来影响,如总线中引入灵活的流水线方式就给系统架构及事务级(Transaction level)设计带来很大的影响。针对总线在IP核互连中存在的一些问题,最近出现了NoC的设计理念。NoC理念的核心是分层互连,将SoC设计中的IP核与互连的线分开来,使得系统的设计优化和IP核的设计优化互不影响。目前已经有利用NoC的设计理念完成了的芯片。

2、片上总线

片上总线是通过仲裁和译码的方式来完成不同主、从部件的互连及总线复用,比较常用的主要有ARM 的AMBA总线、IBM 的CoreConnect总线、Silicore公司的Wishbone总线。

(1)AMBA总线

AMBA定义了三种不同类型的总线:AHB、ASP 和APB。AHB 用于高性能、高数据吞吐部件,如CPU、DMA、DSP 之间的互连,ASP 用来作处理器与外设之间的互连,APB 则为系统的低速外部设备提供低功耗的简易互连。系统总线和外设总线之间的桥接器提供AHB/ASP 部件与APB 部件间的访问代理与缓冲。

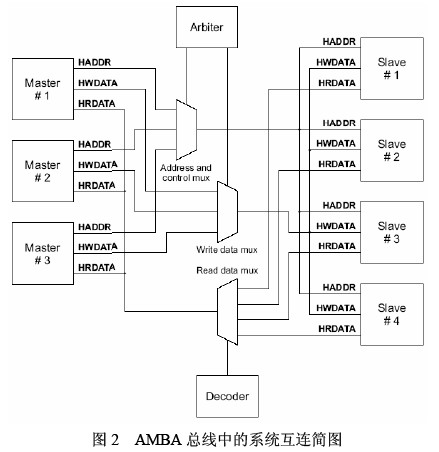

AHB系统是由主方(Master),从方(Slave)和基础部件(Infrastructure)三部分所组成。整个AHB线上的传输都是由主方发出,由从方负责响应。而基础部件则由仲裁器(Arbiter)、主方到从方的多路选择器(master to slave multiplexor)、从方到主方的多路选择器(slave to master multiplexor)、译码器(decoder)等所组成。AHB 支持多个主方,在某个时刻它用仲裁器来仲裁选择一个主方。而译码器则是负责地址的译码,从多个从方中选择要响应主方传输要求的从方。多路选择器负责总线的互连,将总线上的信号在主方和从方进行传送,图2简单说明了它们连结的情形。

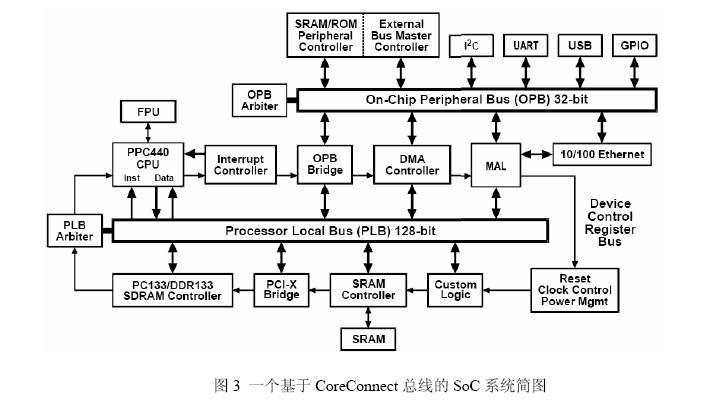

(2)CoreConnect总线

图2 AMBA 总线中的系统互连简图

CoreConnect提供了三种基本类型总线:处理器内部总线(PLB,ProcessorLocal Bus)、片上外围总线(OPB,On-Chip Peripheral Bus)和设备控制总线(DCR,Device Control Register)。其功能及架构与AMBA有异曲同工之处。

(3)Wishbone总线

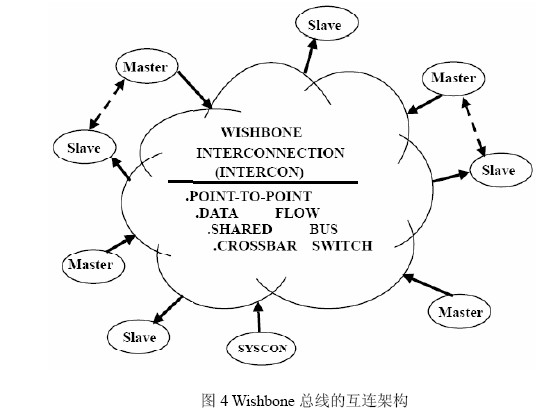

Wishbone采用主/从的构架,主、从方通过点到点(point-to-point)、数据流(data flow)、共享总线(shared bus)、交叉开关(crossbar switch)四种不同形式进行互连,对于内部互连方式用户可灵活选择、生成、扩展。

从以上三种总线的分析看,AMBA和CoreConnect较为相似,而Wishbone已经开始有了内部互连交叉开关的概念,具有了一些片上网络的特性,但因其缺乏分层互连的思想,故仍归入总线一类。

3、片上网络

采用NoC 技术来进行IP 核互连的理念是逐渐演进的,Wishbone 已经初步具备了一些NoC 技术的特性,如交叉开关的概念。

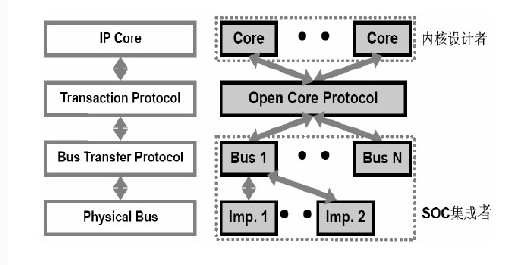

而OCP-IP 的OCP(Open CoreProtocol)协议将IP 核和互连总线通过OCP 界面(interface)分开来,已经具备了层次化互连的理念,因此将OCP 纳入到 NoC 的技术范畴。OCP-IP 的主席IanR.Mackintosh 先生也一再强调OCP 的协议不是总线协议。步OCP-IP 之后,已经有多家公司致力于研究NoC相关的技术和产品,较为突出的几家是法国的Arteris公司、英国的Silistix 公司及美国的Sonics 公司。

(1)OCP-IP 的OCP 协议

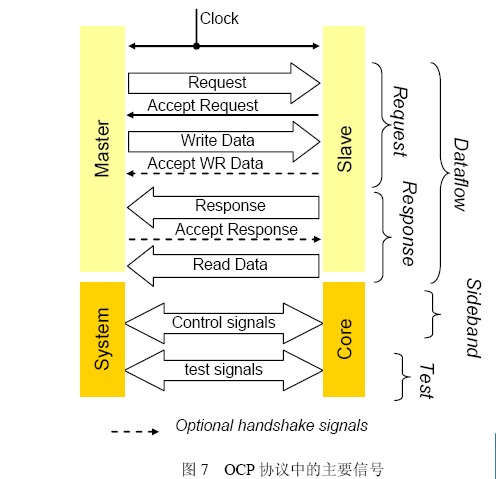

OCP 协议的核心是在IP 核和互连总线之间引入一个事务协议层,如图5 所示,该协议定义了IP核与对应接口模块间点到点的接口信号,除了数据和控制信号,还包括边带控制信号(sideband control)和测试信号,除了时钟外的所有信号都是点到点的同步信号。

1)OCP协议的特性

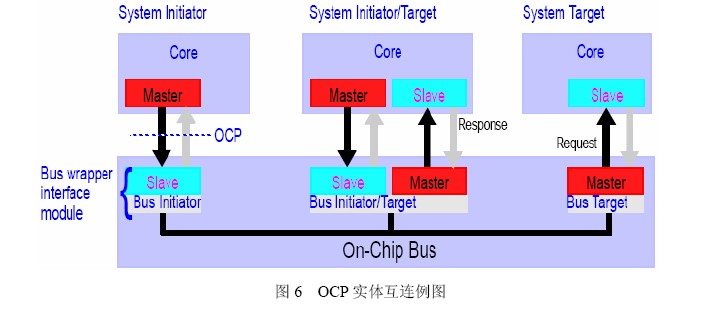

OCP协议在两个互连的实体(entity)间定义了一个点到点(point-to-point)的界面。其中一个实体作为OCP实例的主方,另外一个实体作为从方,只有主方可以发出命令,从方响应主方的命令,或是从主方接受数据,或是将数据传给主方。

图5 OCP 协议的分层互连策略

图6描述了一个包括一个包装总线(wrapped bus)和三个IP核的系统。对于包装总线界面模块而言,他要扮演OCP协议的互补的两个角色,即它既是主方,也是从方。一个传输的流程如下:系统发起方(system initiator)(作为OCP的主方)将控制或数据信息发送给与他互连的从方;总线界面模块将请求(request)在总线上传输(OCP自身不定义总线功能);此处,总线界面模块将请求转换为系统总线的传输;接受的总线界面模块(作为OCP主方)将系统总线的操作转换成合法的OCP命令;系统目标方(system target)(OCP的从方)接到命令并对此作出反应。

2)主要信号

OCP 协议中共有三大类信号:数据流信号(Dataflow signals),边带信号,测试信号(Test signals),如图7 所示。

数据流信号主要包括:基本信号(Basic signals)、简单扩展信号(Simple extensions signals)、突发扩展信号(Burst extensions signals)和线程扩展信号(Thread extensions signals);边带信号主要包括:重置(Reset)、中断(Interrupt)、错误(Error)等信号;测试信号主要包括用于支持扫描(Scan)、时钟控制和IEEE 1149.1(JTAG)的信号,所有的MasterSlave

Request

Write Data

Response

Read Data

Control signals

test signals

System

Core

Accept Request

Accept WR Data

Accept Response

Clock

Dataflow

Request Response

Optional handshake signals

Sideband

Test测试信号都是可选的。

(2)NoC

随着SoC 中信息的传输交换越来越多,采用层次化的互连方法可以很好的解决以总线为中心互连时信息交换的瓶颈问题,目前法国的Arteris 公司、英国的Silistix 公司都推出了NoC 技术相关的产品。

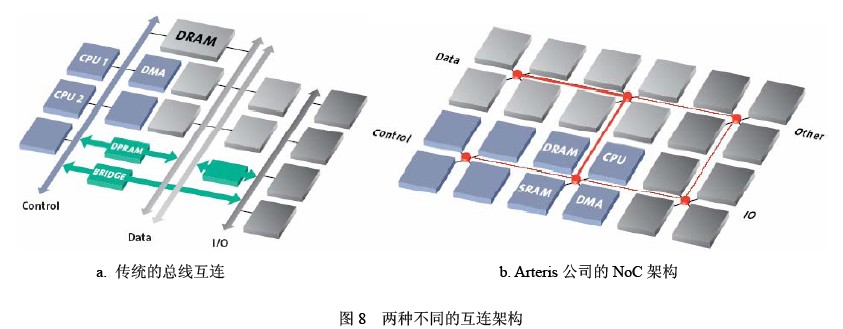

1)NoC 的架构

图8 示意了总线架构和Arteris 公司的NoC 架构,NoC 是一个均匀的、可升级的开关结构网络(switch fabric network),开关结构(switch fabric)(图8 b 中IP 核互连的节点)是NoC 技术的核心,他在复杂的SoC 中传送各种各样的数据包(data packet)

2)NoC 的层次

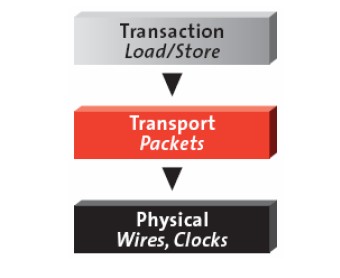

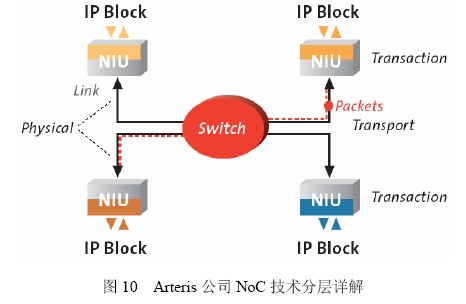

在NoC 技术中,IP 核的互连采用了三层次的互连策略,如图9 所示,他们a. 传统的总线互连 b. Arteris 公司的NoC 架构分别是事务层(Transaction)、传输层(Transport)、物理层(Physical)。

事务层定义了IP 核之间是如何互连交互信息的。如图10 中所示的NoC 界面单元NIU(NoC Interface Units)在IP 核之间提供事务层互连服务,NIU 将IP核和外部的协议(如AHB)隔离开,NIU 在两个协议间转换事务内容。一个典型的NoC 事务是由一个主NIU(master NIU)到从NIU(slave NIU)的请求和从NIU 到主NIU 的应答(response)构成。事务层将信息互换的实现细节留到传输层和物理层实现。传输层定义了在开关结构间传送数据包的规则,在数据包中需要一些信息(例如一般是在数据包的头部)来引导数据包的传输。

数据包的格式是可变的,可以在不影响传输层的情况下很容易的适应事务层的变化。例如数据包可以根据实际应用需求包含字节使能(byte enables)、用户信息等信息,而不需要改变传输规则和物理实现。

物理层则具体定义了数据包是如何通过界面传递的,如此实现了开关结构间的互连可以在带宽、数据完整性等方面进行优化而不会影响到事务层和传输层。

4、总结

工艺的进步和设计方法学的进步使SoC 的设计规模越来越大,所集成的IP核越来越多,由此使得IP 核间的互连显得越来越重要。

除了常见的基于总线的IP 核互连方法,Internet 网络中分层互连的思想也被引入到SoC 中IP 核的互连上来。可以预见,随着技术的进步,将不断有新的互连方法出现。

图9 Arteris 公司的NoC 技术的分层

参考文献

[1]ARM Ltd. AMBA, Advanced Microcontroller Bus Architecture Specification, Rev

2.0, May 1999.

[2]IBM Corporation, CoreConnect Bus Architecture, product brief. URL:

http://www.chips.ibm.com/news/1999/990923/pdf/corecon128_pb.pdf

[3]W.J. Bainbridge, L.A. Plana & S.B. Furber, “The Design and Test of a Smartcard

Chip Using a CHAIN Self-timed Networkon- Chip”, Proc. DATE'04, Vol. 3, Paris,

Feb 2004, p. 274.

[4]T. Felicijan & S.B. Furber, “An Asynchronous On-Chip Network Router with

Quality-of-Service (QoS) Support”, Proc. IEEE International SOC Conference, Santa

Clara, CA, Sept. 2004, pp. 274-277.

[5]OCP Specification, OCP-IP Association

[6]WISHBONE Specification, Silicore Inc.

[7]New IP Integration Strategies Simplify SoC Design, Robin Bhagat

孙加兴

Tel: 86-10-63951881-8112 Mobile: 86-13910951867

Email: sunjx@csip.org.cn URL: http://www.csip.org.cn

Fax:010-86-63973485

信息产业部软件与集成电路促进中心

北京市海淀区羊坊店东路博望园10 号 邮编:100038

本文来源:中国集成电路杂志 作者:信息产业部软件与集成电路促进中心 孙加兴 |

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图