本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

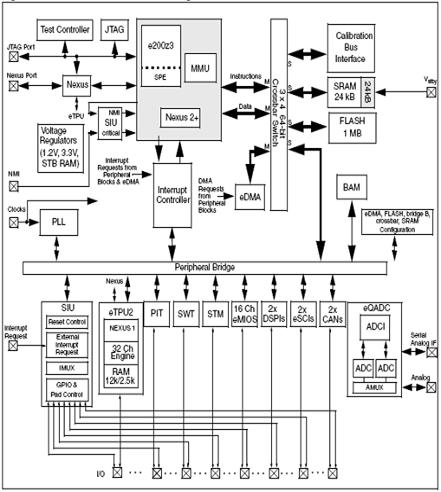

ST公司的SPC563M60是32位基于PowerPC Book E兼容CPU的MCU,适用于汽车动力控制应用.

SPC563M60的用户模式和经典的Power Architecture指令集兼容,具有增强的性能以改善在嵌入式系统中的应用,并具有支持DSP的其它指令,以及集成了增强的时间处理单元,增强排队功能的ADC等.本文主要介绍了SPC563M60的主要特性和方框图.

SPC563M60L5 SPC563M60B2 32-bit Power Architecture based MCU for automotive powertrain applications

The SPC563M60 series microcontrollers are system-on-chip devices that are bui on Power ArchitectureTM technology and:

Are 100% user-mode compatible with the classic Power Architecture instruction set

Contain enhancements that improve the architecture’s fit in embedded applications

Include additional instruction support for digital signal processing (DSP)

Integrate technologies such as an enhanced time processor unit, enhanced queued

analog-to-digital converter.

SPC563M60器件特性:

SPC563M60主要特性:

Feature List

High performance e200z3 core processor

32-bit PowerPC Book E programmer’s model

Variable Length Encoding Enhancements

–Allows PPC instruction set to be optionally encoded in a mixed 16 and 32 bitinstructions

–Results in smaller code size

Single issue, 32-bit PowerPC Book E compliant CPU

In-order execution and retirement

Precise exception handling

Branch processing unit

–Dedicated branch address calculation adder

–Branch acceleration using Branch Lookahead Instruction Buffer Load/store unit

–1 cycle load latency

–Fully pipelined

–Big and Little endian support

–Misaligned access support

–Zero load-to-use pipeline bubbles

Thirty-two 64 bit general purpose registers (GPRs)

Memory management unit (MMU) with 8-entry fully-associative translation look-aside buffer (TLB)

Separate instruction bus and load/store bus

Vectored interrupt support

Interrupt latency < 0 ns @80 MHz (measured from interrupt request to execution of first instruction of interrupt exception handler)

Non maskable interrupt input. For handling external events that must produce an immediate response. Such as power down detection. (May not be recoverable)

Critical Interrupt input. For external interrupt sources that are higher priority than provided by the Interrupt Controller. (Always recoverable) New ‘Wait for Interrupt’ instruction, to be used with new low power modes.

Reservation instructions for implementing read-modify-write accesses

Signal processing extension (SPE) APU

–Operating on all 32 GPRs that are all extended to 64 bits wide

–Provides a full compliment of vector & scalar integer and floating point arithmetic

operations (including integer vector MAC & MUL operations) (SIMD)

–Provides rich array of extended 64 bit loads and stores to/from extended GPRs

–Fully code compatible with e200z6 core

Floating point

–IEEE 754 compatible with software wrapper

–Scalar Single precision in hardware, double precision with software library

–Conversion instructions between single precision floating point and fixed point

–Fully code compatible with e200z6 core

Long cycle time instructions, except for guarded loads, do not increase interrupt latency

Extensive system development support through Nexus debug port

Advanced microcontroller bus architecture (AMBA) crossbar switch (XBAR)

3 master ports, 4 slave ports

–Masters: CPU Instruction bus; CPU Load/store bus (Nexus); DMA

–Slave: Flash; SRAM; Peripheral Bridge; calibration EBI

32-bit internal address bus, 64-bit internal data bus

Enhanced direct memory access (eDMA) controller

32 channels support independent 8, 16 or 32 bit single value or block transfers

Supports variable sized queues and circular queues

Source and destination address registers are independently configured to postincrement or remain constant

Each transfer is initiated by a peripheral, CPU, or eDMA channel request

Each eDMA channel can optionally send an interrupt request to the CPU on completion

of a single value or block transfer

Interrupt controller (INTC)

191 peripheral interrupt request sources, plus 165 reserved positions.

Eight software setable interrupt request sources.9-bit vector

–Unique vector for each interrupt request source.

–Provided by hardware connection to processor or read from register.

Each interrupt source can be programmed to one of 16 priorities.

Preemption

–Preemptive prioritized interrupt requests to processor.

–ISR at a higher priority preempts ISRs or tasks at lower priorities.

–Automatic pushing or popping of preempted priority to or from a LIFO.

–Ability to modify the ISR or task priority. Modifying the priority can be used to implement the Priority Ceiling Protocol for accessing shared resources.

Low latency - three clocks from receipt of interrupt request from peripheral to interrupt request to processor.

Frequency Modulating Phase-locked loop (FMPLL)

Reference clock pre-divider (PREDIV) for finer frequency synthesis resolution

Reduced frequency divider (RFD) for reducing the FMPLL output clock frequency without forcing the FMPLL to re-lock

System clock divider (SYSDIV) for reducing the system clock frequency in normal or bypass mode

Input clock frequency range from 4 MHz to 20 MHz before the pre-divider, and from 4 MHz to 16 MHz at the FMPLL input

Voltage controlled oscillator (VCO) range from 256 MHz to 512 MHz

VCO free-running frequency range from 25 MHz to 125 MHz

Four bypass modes: crystal or external reference with PLL on or off

Two normal modes: crystal or external reference

Programmable frequency modulation

–Triangle wave modulation

–Register programmable modulation frequency and depth Lock detect circuitry reports when the FMPLL has achieved frequency lock and continuously monitors lock status to report loss of lock conditions

–User-selectable ability to generate an interrupt request upon loss of lock

–User-selectable ability to generate a system reset upon loss of lock Clock quality monitor (CQM) module provides loss-of-clock detection for the FMPLL reference and output clocks

–User-selectable ability to generate an interrupt request upon loss of clock

–User-selectable ability to generate a system reset upon loss of clock

–Backup clock (reference clock or FMPLL free-running) can be applied to the system in case of loss of clock

Calibration bus interface (EBI)

1.8 V to 3.3 V ± 10% I/O (1.6 V to 3.6 V)

Memory controller with support for various memory types

16-bit data bus, up to 22-bit address bus

Selectable drive strength

Configurable bus speed modes

Bus monitor

Configurable wait states

System integration unit (SIU)

Centralized GPIO control of 71 I/O pins

Centralized pad control on a per-pin basis

–Pin function selection

–Configurable weak pull-up or pull-down

–Drive strength

–Slew rate

–Hysteresis

–Pin function selection

–Configurable weak pull-up or pull-down

–Drive strength

–Slew rate

–Hysteresis

System reset monitoring and generation

External interrupt inputs, filtering and control

Critical Interrupt control

Non Maskable Interrupt control

Internal multiplexer subblock (IMUX)

–Allows flexible selection of eQADC trigger inputs (eTPU, eMIOS and external signals)

–Allows selection of interrupt requests between external pins and DSPI

Error correction status module (ECSM)

Configurable error-correcting codes (ECC) reporting

On-chip FLASH

1 Mbyte flash memory, accessed via a 64 bit wide Bus Interface

Fetch Accelerator

–Provide single cycle flash access @80 MHz

–Quadruple 128 bit wide prefetch/burst buffers

–Prefetch buffers can be configured to prefetch code or data or both Censorship protection scheme to prevent flash content visibility

Hardware read-while-write feature that allows blocks to be erased/programmed whileother blocks are being read. (used for EEPROM emulation & data calibration)10 blocks (2 x 16 Kbytes, 2 x 48 Kbytes, 2 x 64 Kbytes, 2 x 128 Kbytes, 2 x 256 Kbytes) to support features such as boot block, operating system block and EEPROM emulation.

Hardware programming state machine

On-chip static RAM

48 Kbyte general purpose RAM of which 24 Kbytes are on standby power supply

Boot assist module (BAM)

Enables and manages the transition of MCU from reset to user code execution in the following configurations:

–Execution from internal flash memory

–Download and execution of code via FlexCAN or eSCI

Periodic interrupt timer (PIT)

32-bit wide down counter with automatic reload

4 channels clocked by system clock

1 channel clocked by crystal clock

Each channel can produce periodic software interrupt

4 out of the 5 can produce periodic triggers for eQADC queue triggering

1 out of the 5 can be used as wake-up timer to wake device from low power stop mode

System timer module (STM)

32 bit up counter with 8 bit prescaler

clocked from system clock

4 channel timer compare hardware

Each channel can generate a unique interrupt request

Design to address AutoSAR task monitor function

System watchdog timer

32 bit timer

clock by system clock or crystal clock

can generate either system reset or non maskable interrupt followed by system reset

Enabled out of reset

Enhanced modular I/O system (eMIOS)

16 standard timer channels (Up to 14 channels connected to pins in LQFP144)

24 bit timer resolution

Supports a subset of the timer modes found in eMIOS on MPC5554

Three selectable time bases plus shared time or angle counter bus

DMA and interrupt request support

Motor control capability

Second Generation Enhanced time processor unit (eTPU2)

High level assembler/compiler

Enhancements to make ‘C’ compiler more efficient

New ‘engine relative’ addressing mode

32 channels (Each channel has dedicated IO pin in LQFP144)

24-bit timer resolution

TCR1 run at full system clock speed for improved resolution

12 Kbytes code memory and 2.5 Kbytes data memory

Variable number of parameters allocatable per channel

Double match/capture channels

Angle clock hardware support

Nexus Class 1 Debug support

Enhancements to make DMA & interrupt operation more flexible

New programmable channel mode, for increased flexibility of channel hardware

Enhanced queued A/D converter (eQADC)

Two independent on-chip RSD Cyclic ADCs

–8, 10, and 12 Bit AD Resolution

–Targets up to 10 bit accuracy at 500KSample/s (ADC_CLK=7.5MHz) and 8 bit accuracy at 1MSample/s (ADC_CLK=15MHz) for differential conversions

–Differential conversions

–Differential channels include variable gain amplifier for improved dynamic range (x1; x2; x4)

–Differential channels include programmable pull-up and pull-down resistors for biasing and sensor diagnostics (200k ohms; 100k ohms; 5k ohms)

–Single-ended signal range from 0 to 5V

–Sample times of 2 (default), 8, 64 or 128 ADC clock cycles

–Provides time stamp information when requested

–Parallel interface to eQADC CFIFOs and RFIFOs

–Supports both right-justified unsigned and signed formats for conversion results

–Temperature sensor.

–Ability to measure directly Vdd.

Automatic application of ADC calibration constants

– Provision of reference voltages (25%VREF1 and 75%VREF) for ADC calibration purposes

32 input channels available to the two on-chip ADCs

4 pairs of differential analog input channels

Full duplex synchronous serial interface to an external device

–Has a free-running clock for use by the external device

–Supports a 26-bit message length

–Transmits a null message when there are no triggered CFIFOs with commands bound for external CBuffers, or when there are triggered CFIFOs with commands bound for external CBuffers but the external CBuffers are full.

Parallel Side Interface to communicate with an on-chip companion module Priority Based CFIFOs

–Supports six CFIFOs with fixed priority. The lower the CFIFO number, the higher its priority. When commands of distinct CFIFOs are bound for the same CBuffer, the higher priority CFIFO is always served first.

–Supports software and several hardware trigger modes to ARM a particular CFIFO

–Generates interrupt when command coherency is not achieved

External Hardware Triggers

–Supports rising edge, falling edge, high level and low level triggers

–Supports configurable digital filter

Supports 4 external 8-to-1 muxes which can expand the input channel number from 31to 59

2 deserial serial peripheral interface modules (DSPI)

SPI

–Full duplex communication ports with interrupt and DMA request support

–Supports all functional modes from QSPI subblock of QSMCM (MPC5xx family)

–Support for queues in RAM

–6 Chip Selects, expandable to 64 with external demultiplexers

–Programmable frame size, baud rate, clock delay and clock phase on a per frame basis

–Modified SPI mode for interfacing to peripherals with longer setup time requirements

–LVDS option for output clock and data to allow higher speed communication Deserial serial interface (DSI)

–Pin reduction by hardware serialization and deserialization of eTPU, eMIOS channels and GPIO

–32 bits per DSPI module

–Triggered transfer control and change in data transfer control (for reduced EMI)

–Compatible with Microsecond Bus Version 1.0 downlink

2 Enhanced serial communication interface (eSCI) modules

UART mode provides NRZ format and half or full duplex interface

eSCI bit rate up to 1 Mbps

Advanced error detection, and optional parity generation and detection

Word length programmable as 8, 9, 12 or 13 bits

Separately enabled transmitter and receiver

LIN support

DMA support

Interrupt request support

Programmable clock source: system clock or oscillator clock

Support Microsecond Bus (Timed Serial Bus - TSB) uplink Version 1.0

2 FlexCAN

One with 32 message buffers; the second with 64 message buffers

Full implementation of the CAN protocol specification, Version 2.0B

Based on and including all existing features of the Freescale TouCAN module

Programmable acceptance filters

Short latency time for high priority transmit messages

Arbitration scheme according to message ID or message buffer number

Listen only mode capabilities

Programmable clock source: system clock or oscillator clock

Message buffers may be configured as mailboxes or as FIFO

Nexus port controller (NPC)

Per IEEE-ISTO 5001-2003

Real time development support for PowerPC core and eTPU engine through Nexus class 2/1

Read and write access (Nexus 3 feature that is supported on this device)

–Run-time access of entire memory map

–Calibration

Support for data value breakpoints / watchpoints

–Run-time access of entire memory map

–Calibration

Table constants calibrated using MMU and internal and external RAM

Scalar constants calibrated using cache line locking Configured via the IEEE 1149.1 (JTAG) port

IEEE 1149.1 JTAG controller (JTAGC)

IEEE 1149.1-2001 Test Access Port (TAP) interface

A 5-bit instruction register that supports IEEE 1149.1-2001 defined instructions

A 5-bit instruction register that supports additional public instructions

Three test data registers: a bypass register, a boundary scan register, and a device

identification register

Censorship disable register. By writing the 64 bit serial boot password to this register,

Censorship may be disabled till the next reset.

A TAP controller state machine that controls the operation of the data registers,instruction register and associated circuitry

On-chip Voltage Regulator for single 5 V supply operation

On chip regulator 5 V to 3.3 V for internal supplies and Nexus interface

On chip regulator controller 5 V to 1.2 V (with external bypass transistor) for core logic Low Power Modes

SLOW Mode. Allows device to be run at very low speed (approximately 1 MHz),with modules (including the PLL) selectively disabled in software.

STOP Mode. System clock stopped to all modules including the CPU. Wake-up timer used to restart the system clock after a predetermined time.Package

Available in 100 QFP, LQFP144 (20mm x 20mm, 0.5mm pitch), LBGA208 and 496 BGA (for calibration tools)

图1.SPC563M60系列方框图 |

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图