本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

摘 要: 在介绍I2C总线协议的基础上,讨论了基于CPLD的系统中I2C总线的设计技术,并结合工程实例设计了I2C总线IP核,给出了部分源代码和仿真结果。

关键词: I2C总线 IP核 CPLD

I2C总线是PHILIPS公司推出的新一代串行总线,其应用日渐广泛[1~2]。目前许多单片机都带有I2C总线接口,能方便地实现I2C总线设计;对没有I2C总线的微控制器(MCU),可以采用两条I/O口线进行模拟。在以单片机为MCU的系统中很容易实现I2C总线的模拟扩展,有现成的通用软件包可以使用[2~3]。

对有些基于CPLD的系统,要与带有I2C总线接口的外围器件连接,实现起来相对复杂一些。为实现系统中的I2C总线接口,可以另外引入单片机,也可以采用PCF8584或者PCA9564器件(PHILIPS公司推出的专用I2C总线扩展器)进行扩展,但这样会增加系统成本,使系统冗余复杂。像ALTERA、XILINX等一些大公司有专用的基于CPLD器件的I2C总线IP核,但这些IP核的通用性不强,需要的外围控制信号较多,占用系统很大的资源,因此直接采用这种IP核不可取。

鉴于此,依照I2C总线协议的时序要求,在基于CPLD的系统中开发了自己的I2C总线IP核。对于一些带有I2C总线接口的外围器件较少、对I2C总线功能要求较简单的CPLD系统,自主开发IP核显得既经济又方便。

1 I2C总线的协议[1]

I2C总线仅仅依靠两根连线就实现了完善的全双工同步数据传送:一根为串行数据线(SDA),一根为串行时钟线(SCL)。该总线协议有严格的时序要求。总线工作时,由时钟控制线SCL传送时钟脉冲,由串行数据线SDA传送数据。总线传送的每帧数据均为一个字节(8 bit),但启动I2C总线后,传送的字节个数没有限制,只要求每传送一个字节后,对方回应一个应答位(Acknowledge Bit)。发送数据时首先发送数据的最高位(MSB)。

I2C总线协议规定,启动总线后第一个字节的高7位是从器件的寻址地址,第8位为方向位(“0”表示主器件对从器件的写操作;“1”表示主器件对从器件的读操作),其余的字节为操作的数据。总线每次传送开始时有起始信号,结束时有停止信号。在总线传送完一个或几个字节后,可以使SCL线的电平变低,从而使传送暂停。

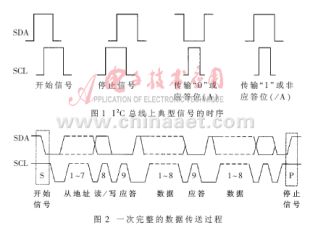

图1列出了I2C总线上典型信号的时序,图2表示I2C总线上一次完整的数据传送过程。

依据I2C总线的传输协议,总线工作时的具体时序如下:

起始信号(S):在时钟SCL为高电平期间,数据线SDA出现由高电平向低电平的变化,用于启动I2C总线,准备开始传送数据;

停止信号(P):在时钟SCL为高电平期间,数据线SDA出现由低电平向高电平的变化,用于停止I2C总线上的数据传送;

应答信号(A):I2C总线的第9个脉冲对应应答位,若SDA线上显示低电平则为总线“应答”(A),若SDA线上显示高电平则为“非应答”(/A);

数据位传送: I2C总线起始信号或应答信号之后的第1~8个时钟脉冲对应一个字节的8位数据传送。在脉冲高电平期间,数据串行传送;在脉冲低电平期间,数据准备,允许总线上数据电平变化。

2 应用实例

2.1 实例模型介绍

现举某应用实例,要求对显示器的视频信号进行采集、处理和再显示,整个系统采用CPLD器件进行控制。信号采集采用A/D公司的专用视频采集芯片AD9883,该芯片在使用前需要依据实际的功能指标进行初始化。初始化过程依靠AD9883的SDA和SCL两引脚进行。在系统中用CPLD器件(ALTERA公司的EPM3256A)实现初始化:按照I2C总线协议向AD9883的19个内部寄存器(01H~13H)写入19组固定的8位数据;第14H寄存器为只读型同步检测寄存器,仅用于检测几个关键的数据设置。

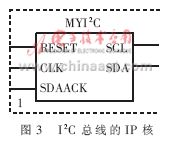

可见该I2C总线模型如下:单主操作,只实现简单的写和读操作(亦可只有写操作,只是硬件调试的时候会麻烦些),写地址连续,没有竞争和仲裁,是很简单的I2C总线系统。由此设计了如图3所示的IP核。其中,RESET为复位信号,CLK为系统时钟。

为了软件仿真方便,把双向数据线SDA用分离的两条线模拟:SDA为数据输出,SDAACK为SDA的应答信号。软件仿真成功后,只要把SDA设置为双向,稍微修改一下程序就可以向CPLD器件下载,进行实际应用。

对AD9883内部地址连续的寄存器进行初始化,I2C总线上传输的时序信号依次为:开始信号(S);从器件地址和写操作位(SLAW);内部寄存器基地址(Base Address);写入基地址的数据(Data0);写入下一地址(Base Address+1)的数据(Data1);写入地址(Base Address+2)的数据(Data2);……;写入地址(Base Address+18)的数据(Data18);停止信号(P)。

针对AD9883,如果电路中的A0引脚(55#)接电源,则SLAW=“10011001”;Base Address=“00000001”,Data0~Data18是依据实际需要写入的初始化数据。

2.2 IP核程序的编写

整个程序用VHDL语言编制,SCL输出时钟的设计是基于CLK输入时钟的64分频的。程序由三个状态组成:开始(START)、转换(SHIFT)和应答(ACK)。状态定义如下:

type states is (start,shift,ack);

signal my_states :states;

下面给出部分进程的源代码以供参考。

2.2.1 开始信号的产生

PROCESS(clk)

if clk’event and clk=‘1’ then

TWCR<=DATAIN;

SCL<=‘1’;

else

TWCR<=(others=>‘0’);

end if;

if TWCR=“10000000” then --比较寄存器TWCR的开始值设置(由用户决定)

STRB<=‘1’;

end if;

if STRB=‘1’ then --开始条件

INT<=INT+“000001”; --INT为时钟脉冲计数

if INT<=“011000” then --产生SDA的下降沿

SDA<=‘1’;

else

SDA<=‘0’;

end if;

if INT>=“011110” then --STRB归0,保证只产生一次开始信号

STRB <=‘0’;

INT<=“000000”;

end if;

end if;

等所有的初始化数据传输完毕后即产生停止信号,过程与上面相类似,在此省略。

2.2.2 数据转换过程

数据转换过程采用移位传输,传输8位之后即进入应答状态。

when shift=>

if cnt=“010000” then --cnt为clk脉冲计数,由实际的时钟频率决定cnt的值

COUNT<=COUNT+“0001”; --COUNT为数据移位个数计数,MSR为移位寄存器

MSR<=MSR(6 downto 0)&txtag;

txtag<=‘0’;

if COUNT=“1000” then

my_states<=ack;

TACK<=‘1’; --TACK为应答标志位

else

SDA<=MSR(7);

my_states<=shift;

TACK<=‘0’;

end if;

end if;

2.2.3 数据输入

一般情况下,I2C总线传输的数据要由外部ROM或其它专门的数据存储区来存储,但在数据相对固定且数据量不是很大的情况下,可以将初始化的数据写在程序中,这样可减少频繁的数据交换,简化操作。AD9883的初始化数据就属于这种情况,可以通过检测应答信号来改变输入的值。程序如下:

PROCESS(clk) --数据输入

if clk’event and clk=‘1’ then

CASE ackint IS --ackint为应答计数,每应答一次,输入改变一次

when “00000”=> DATAIN<=“10000000”;

when “00001”=> DATAIN<=“01010010”;

when “00010”=> DATAIN<=“11010000”;

……

when “10010”=> DATAIN<=“00000000”;

when “10011”=> DATAIN<=“00000000”;

when others=> DATAIN<=“ZZZZZZZZ”;

END CASE;

end if;

2.3 仿真结果

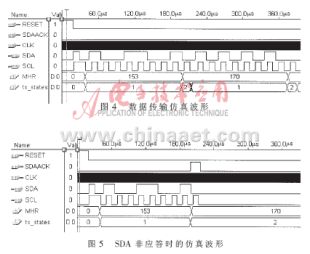

把自主开发的IP核置于MAX+PLUS II 10.0开发环境下,选用EPM3128ATC100-10器件,经过编译、调试与仿真,证明该程序符合设计要求。图4是模拟产生开始信号并传输两组二进制数据“10011001”和“10101010”(十进制表示为153和170)的仿真波形。图5是传输数据“10011001”后没有应答时的仿真结果,此时总线处于暂停状态。

仿真完成后,通过编程电缆将pof文件下载到实际电路的EPM3128ATC100-10中,然后对AD9883进行初始化,结果工作正常,这进一步验证了采用该自主开发的IP核完全可满足I2C总线的时序要求,能实现I2C总线的功能。

参考文献

1 The I2C-Bus Specification Version 2.1. Philips Semiconductors, January 2000

2 何立民. I2C总线应用系统设计. 北京:北京航空航天大学出版社,1995

3 何立民.按平台模式设计的虚拟I2C总线软件包.单片机与嵌入式系统应用,2001(2)

4 李明峰,李沁遥.I2C器件接口IP核的CPLD设计. 单片机与嵌入式系统应用,2003(1)

5 I2C总线的串行扩充技术.http://www.zlgmcu.com

6 http://www.opencores.org/projects/i2c |

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图