本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

1 引言

数字图像处理理论和技术的飞速发展使得大多数图像处理的问题都转变为用数字信号处理的形式来解决。数字图像处理有两大优势:第一、数字信号处理中存在大量成熟的快速算法,如:FFT,FHT等,这些算法大量的应用到图像处理中;其次,随着超大规模集成电路的发展,DSP的处理速度,内部存储器容量等等大大提高,为实时图像处理提供了最优的解决方式,这就是DSP + FPGA 相结合的设计方式。这种方式下,用一片高速DSP完成图像处理算法,然后利用FPGA 的在控制和协作处理上的优势,将DSP 从控制回路中解脱出来,全力投入到运算中,能够获得最高的工作速度和稳定性。

2 系统简介

我们所设计的系统的结构如图1。该系统是自主移动机器人无线遥控遥测系统双目视觉部分。这个系统包括两个架设在云台上的摄像头,它拍摄被跟踪目标的图像,通过视频解码 器SAA7115H处理后送入DSP ,DSP 通过这些图像信息,判断出被跟踪物体的运动方向,相对速度,把每帧图像处理后,提取出来的特征值(位置,速度等运动状态信息) 送到FPGA ,FPGA 通过无线模块ptr8000 把这些信息发送到控制台,控制台通过被跟踪物体运动状态的改变,控制机器人调整自己的运动状态,进行跟踪。

系统原理图

3 系统硬件设计

3. 1 方案论证

DM642 是TI 公司推出的针对多媒体处理领域应用的DSP(主频600M) ,有4800MIPS 的峰值计算速度。我们采取每秒钟处理6 帧图像,那么处理每帧图像的时间就为0. 1667s , 这段时间DM642 能完成的最大指令个数是800M条,我们采集的每个图像是320 3 240 像素的16 位RGB 图像,则每一幅图像的大小约是300Kbit,每次同时处理两帧图像,两帧图像也就是4 幅1.2Mbit ,我们对采集到的图像要进行图像预处理、图像去噪、边缘检测、最后完成匹配。图像预处理对图像的每一个像素点进行一次加乘运算,生成灰度图像,这个过程的 运算量大约为图像像素值的3倍,大约1M。图像去噪的算法我们采用移动平均法,计算量约为像素值的10 倍,大约4M。边缘检测算法采用Rob2erts 算子,这个过程运算量比较大,但是不超过100 倍像素值,小于40M,匹配时我们这是将边缘上的交叉点提取出来进行运算,运算量很小。加上特征提取,整个运算量不到50M,而我们最高能够获得800M 的处理能力,所以DM642 的计算能力完全胜任这个项目中的算法,而且为系统提供了很大的裕量。

3. 2 硬件结构

整个系统硬件有DM642、XC2S300E ( FPGA) 、视频解码器SAA7115H、32M SDRAM、4M FLASH、电源管理芯片TPS54310PWP、无线模块PTR8000。DM642 提供了64 位宽的数据线,所以我们将两个内存模块MT48LC4M32B2 共用一组地址线,而数据线分别接到DM642 的高32 位和低32 位数据线上,这样就获得了64位数据总线宽度。FLASH 存储器的低八位也接到这组数据线上,由于FLASH存储器在系统初始化完毕后和DM642 之间没有数据交换,所以在实验过程中没有总线冲突的情况发生。

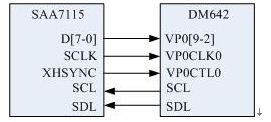

系统需要两路视频输入,所以在设计中我们采用了两片视频采集卡分别连接到了DM642 的视频端口0 和1。初始化配置两片采集卡采用I2C 总线(时钟线SCL和数据线SDL) 。图像数据的传输使用D[7 -0 ] ,由SAA7115 提供同步时钟信号SCLK和XHSYNC。第一片采集卡和DM642 视频端口0 连接方式示意图如图2 ,第二片采集卡和端口1 的连接方式相同,只是共用配置线SCL 和SDL。

图2 DSP 与视频解码芯片SAA7115 连接图

系统的控制完全由FPGA 来完成,我们使用它来实现以下功能:执行中断逻辑控制,和DSP 之间通信,传输DSP 提取出的运动状态特征值;用于实现系统各部分的粘合逻辑;

FPGA 的内部寄存器映像在DSP 的地址空间上,可通过对寄存器的读写来配置系统参数;控制板子上的调试指示灯。设计中FPGA 芯片我们选用Xilinx公司的XC2S300E。我们为它扩展了一片专门的初始化芯片XCF02S ,存放它的初始化配置程序和整个系统的逻辑控制程序。

DM642 的内核电压是1. 4V ,IPO 电压是3. 3V。而且上电、掉电次序有严格的要求,应当保证内核电源(CVDD) 先上电。原因在于:如果外部IPO引脚先上电,芯片缓冲P驱动部分的晶体管将在一个未知状态下工作,这是非常危险的。因此,我们选用了TI 公司专用的电源管理芯片TPS54310PWP ,它可以同时产生上述两种电压。我们用下面的连接方法解决了上电次序的问题:把1. 4V 模块的电源输出有效引脚PG(power good) 连接到3.3V 模块的允许电压输入引脚EN。这样,只有当1. 4V 电压有效之后,3. 3V 电压才开始上电,这就保证了DM642 的内核电压先于IPO 电压上电。另外,系统中的采集卡芯片SAA7115 需要模拟和数字两种电源。我们使用了一个磁珠和另外一片电源管理芯片配合产生了模拟3.3V 电压,为了避免两片电源管理芯片之间的电源噪声互相干扰,我们将两个电源芯片分开设计,模拟地和数字地也分开设计,在一点接地。

3. 3 设计原则

DM642 的工作频率达到600M,属于高频电路,对于高频电路设计中应该注意的是:

(1)采用多层板既是布线所必须的,也是降低干扰的有效手段。

(2) 高速电路器件管脚间的引脚弯折越少越好。高频电路布线的引线最好采用全直线,需要转折,可用135°折线或圆弧转折,这样可以减少高频信号对外的发射和相互间的耦合。

(3) 高频电路器件管脚问的引线越短越好。

(4) 元件连接过程中所用的过孔(Via) 越少越好。我们发现,一个过孔可带来约0. 5PF 的分布电容,减少过孔数能显着提高速度。

(5) 电源层、地线层间隔。各类信号走线不能形成环路,地线也不能形成电流环路。

(6) 高速接口部分如SDRAM加去藕电容。

4 系统的软件设计

TI 提供的基础软件包括CSL (Chip Support Library) 芯片支持库,DDK(Driver Development Kit) 设备驱动程序开发包,DSPLIBPIMGLIB, DSPPBIOS 嵌入式实时、多任务操作系统, ReferenceFrameworks 程序参考架构,XDAIS(DSP 算法标准)。

DSPPBIOS 是最重要的开发工具。它的代码大约1KWords、CPU 占用率1MIPS ,这对我们的系统和DM642 的运算能力来说,是微不足道的开销,但对我们的软件系统来说,它为我们搭建了一个非常优秀的操作系统平台:它有一个基于优先级的、抢先型的实时调度程序; 它能够提供内存管理,实现动态存储器分配。

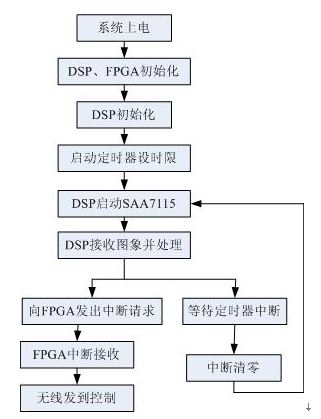

系统流程图如图3:

系统流程图

在DSP 系统上电复位以后,TMS320DM642 开始自举启动过程,将存放在Flash 中的程序代码和初始化数据加载到目标存储空问中。加载完成以后,自举程序跳转到正常程序入口处,并开始执行(Bootload)。

5 系统调试

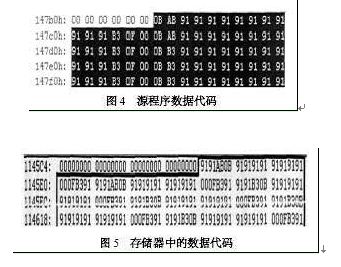

(1)JTAG接口测试我们利用CCS 工具将一部分程序写入SDRAM,然后查看存储器中相应部分写入的数据。图4 是原程序的数据代码,图4- 4 是写入SDRAM后,查看数据的结果。在图4中阴影部分的数据与在图5 中黑粗线所包围的数据一样,如: 图4 中地址000147c2H到000147c5H处四个字节的数据依次是:91 ,B3 ,0F ,00。而在图5 中地址是001145E0H - 001145E3H 处的四个字节的数据是91 ,B3 ,OF ,00。(注意:数据在存储器中的存放顺序有大端和小端两种模式,所谓小端模式指低字节数据存放在内存低地址处,高字节数据存放在内存高地址处;大端字节 序是高字节数据存放在低地址处,低字节数据存放在高地址处。我们选择了DM642 的小端模式,所以两个图是做记号的部分完全对应的)。下图的结果证明JTAG接口已经工作正常,以下的工作就是通过JTAG接口进行其它程序的调试了。

系统调试

(2) RS232 接口测试串口的测试主要借助了串口精灵和计算机中超级终端的帮助,通过系统主机发送一些数据,看串口精灵接受是否正确,反之亦然。调试串口的程序如下:

//init INTCINTC

Init () ;PP初始化中断控制器寄存器;{

UART-ConfigData uart0 ;

uart0. baudRate = UART 115200 ;

uart0. charLength = UART CHAR LEN 8 ;

uart0. stopBits = UART STOPBIT1 ;

uart0. parity = UART NO PARITY;}

//设定基本的通讯参数

sprintf (UART-outBuff ,”\ r \ n \ n DSPFPGA”) ;

UART sendString(UART0 ,UART outBuff) ;

//发送字符串变量DSPFPGA 到串口0

yb = UI getInput () ;

switch(yb)

{case’1’:

DraftPreview(TURE) ;

break ;

case’2’

STILL MENU run() ;

default :

break ;

}

6 结论

为了验证这个系统的满负荷工作能力,我们采用了DSP 连续采集处理的方式,试验结果表明,在我们未做软件优化的条件下,每秒钟可以采集并处理完12 帧图像。而在PC + 采集卡模式上运行程序时,PC 机每秒钟只能处理并发送2 帧双目图像的信息。综上所述,DM642 + FPGA 的实时图像处理系统具有PC机无法比拟的高速性,必将在以后广泛流行起来。 |

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图