本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

目前采用的LED大屏幕显示系统的控制电路大多由单个或多个单片机及复杂的外围电路组成,单片机编程比较复杂,整个电路的调试比较麻烦,可靠性和实时性难以得到保证。针对这种情况,本文提出了一种基于SPCE061A和Cyclone EP1C6的LED大屏幕解决方案。该设计方案无须外挂FLASH ROM和RAM,无须任何外部功能电路,所有功能均由一片EP1C6和一片SPCE061A实现,数据处理速度快、可靠性高。

SPCE061A和CycloneEP1C6简介

SPCE061A是凌阳科技的一款16位微控制器,内嵌32KB闪存和2KB字SRAM。CPU最高可工作在49MHz的主频下,较高的处理速度使SPCE061A能够非常容易、快速地处理复杂的数字信号。本文设计的是一个点阵大小为192×128的单色(红色)显示屏,且按要求连续显示5屏数据,SPCE061A丰富的片内资源正好满足了如此大的数据处理和存储要求。本文采用由UART中断接收上位机数据并将数据写入32KB闪存中的方法,取代了传统MCU+ROM+RAM的设计,增加了系统的稳定性。

Cyclone EP1C6是Altera推出的一款高性价比FPGA。该器件提供的具有异步、双端口、带寄存器输入口、可选择的带寄存器输出口的存储模块-M4K在本设计中被设置成一个双口RAM,实现数据的读写同步,提高了系统的刷新频率。

整体设计方案

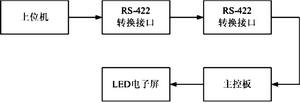

本系统设计的是一块具有192×128个红色LED点阵的电子大屏幕。整块大屏幕是模块化的结构,每4个16×16的点阵块为一个最小模块,每行点阵由3个同样的最小模块级联而成,共8行。大屏幕上要求连续显示5屏内容,且每屏都具有上下左右移动等动画效果。实际应用中主控制室距离电子屏约为200米。结合设计对象的要求和大屏幕设计的特点,本文提出了一种新颖的设计方案。该方案的整体框图如图1所示。

图1 系统框图

LED大屏幕系统由3个主要单元组成:上位机图像/文字编辑与发送部分单元、主控板单元、显示驱动电路单元。系统上位机由一台PC机来控制,它主要编辑、发送图像/文字信息到主控板的存储器中;主控板对这些字模数据进行处理后发送到大屏幕,并在大屏幕上显示出来。

系统硬件设计

上位机发出的信息经符合RS-422标准的接口通过双绞线传送到主控板上,通讯速率可在上位机软件中设置。接口所用芯片为MC3487和MC3486,RS-422在传输速率为100kb/s时,可传输的最大距离为1200米。本系统的传输距离约为200米,传输速率最大为115kb/s,采用RS-422方式传输可满足这一长距离通讯的要求。

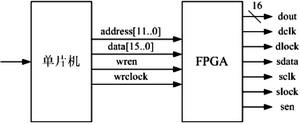

主控板单元设计

该单元的设计特点在于数据流接收、存储以及驱动扫描的单片集成,无须任何外围电路。主控板由一片SPCE061A和EP1C6组成,如图2所示。

&

nbsp; 图2 主控板框图

该单元的设计思路是,由单片机的IOB7口以UART中断的方式接收上位机发送的数据。这是由于大屏幕处于被动、循环往复的显示状态,采用异步传输能减少系统不断查询串口接收标志位的系统消耗。单片机将接收的串口数据以两个字节为单位逐一写入内置的闪存中。单片机内部的2KB SRAM作为缓存区,每当单片机要向FPGA中写一屏新的数据时,先按特定的地址从闪存中读出数据并存放到SRAM中,再将SRAM中的数据并行写到FPGA的双口RAM中。单片机与FPGA的接口信号除了16根数据线外,还包括单片机向FPGA写数据的地址、写使能和写时钟。由于每屏的点阵数为192×128,16位数据并行传输所需的地址线为11根。但由于设计需要,系统中还专门设置了1根额外的地址线,用于对FPGA的双口RAM进行读写分区,因此共使用了12根地址线。

FPGA在其内部配置一个双口RAM缓存单片机写入的数据,同时将这些数据按照大屏幕的结构和扫描电路的特点选择性地读出,然后对数据由并转串输出到大屏幕的扫描驱动电路。由于大屏幕采用模块化的隔行扫描方式,每行需要2根数据线进行隔行传输,整块大屏幕共需16根数据线。由于点阵的行列驱动均采用74LS595驱动,故FPGA还应产生列扫描的点时钟、锁存信号和行扫描的数据、时钟、锁存信号。

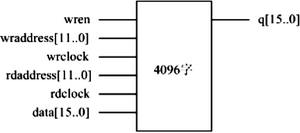

双口RAM的配置

由于数据显示是一种动态扫描方式,如果采用一个RAM区,当单片机写RAM 时,FPGA只能处于等待状态,这样就会导致屏幕动态扫描停止。由于屏幕数据是移位输出的,当扫描停止时,因为会有某一行的高电平保持较长的时间,该行就会一直保持较强的亮度,影响屏幕的显示效果。本系统中设计了2个同样大小的RAM 区:A区和B区,让单片机交替进行写操作。当单片机在写A区时, FPGA就去读B区的字模数据;当单片机写B区时,FPGA就去读A区的字模数据。这样就不会造成FPGA的停止扫描,保证了各行的点阵有相同的时间占空比,使屏幕点阵有同样亮度。单片机中的 HIGHADR引脚可用于控制单片机的写区和FPGA的读区。

由于每屏点阵数据的大小为1536字,A区和B区的容量都至少要大于1536,那么整个的RAM区至少为1536×2字。考虑到EP1C6内部集成了20块容量为256字的M4K模块,正好可以满足本系统对RAM的需求。双口RAM的配置如图3所示。

图3 双口RAM配置

其中wren是单片机往FPGA中写入数据的写使能信号,wraddress[11..0]是写地址信号, wrclock是写时钟,data[15..0]是写数据,rdaddress[11..0]是读地址信号,rdclock是读数据的时钟信号,q[15..0]是读出的数据。对于这个双口RAM而言,只有q[1

5..0]是输出端口,其它均为输入端口。与写数据相关的信号全部由单片机产生,读数据的所有信号由FPGA产生。其中读写地址的最高位可实现RAM分区。

点阵驱动电路

本系统中LED的灰度等级是采用调制占空比的方法来实现的,由于大屏幕是单色点阵,主要用来显示文字信息,所以要求亮度高且均衡。根据这一特点,采用了模块化的隔8行扫描方式。每隔8行点阵同时进行扫描,则每行的占空比是1/8,使屏幕亮度得到保证。

点阵的驱动电路分为行驱动和列驱动,列驱动采用串行数据传输方式,易于模块化。列驱动电路由74LS595组成,行驱动电路由74LS595和与之配套的反相器7406、PNP达林顿功率三极管TIP127组成。所有作为行驱动74LS595的数据时钟信号、数据锁存信号、扫描数据、时钟、锁存信号都在一起,所有作为列驱动74LS595的数据时钟信号、数据锁存信号、扫描数据、时钟、锁存信号也是在一起的,这样可以实现大屏幕的同步显示。

软件设计

系统的软件设计由3部分组成:上位机图像/文字编辑与发送软件设计、单片机控制单元软件设计,以及FPGA控制单元软件设计。

上位机软件设计

上位机的图像/文字编辑与发送软件由Visual Basic编写,只须在界面中将屏幕大小设置为192×128,串口选择COM1或COM2,波特率设置为9600,并设置每屏的起始地址和要发送的屏数,调入包含相关信息的文件,点击“发送”按钮即可。数据流经符合RS-422标准的双绞线传输到主控板。该软件适用于任何大小的彩色/单色屏,提供了丰富的图形/文字编辑、修改功能。也可以直接调用Windows中的16色画图文件(*.bmp),从而可以利用Windows或基于Windows的各种作图工具设计出丰富多彩的图像。

单片机控制单元软件设计

单片机控制单元的软件设计主要实现3大功能:串行数据接收、数据输出和图像显示方式变换。设计流程如图4所示。串行数据接收部分主要是通过UART中断接收并保存位图文件。图像显示方式变换部分实现图像的变换,如上移、下移、左移、右移等,以实现丰富多彩的图像显示效果。

图4 主程序流程图和中断程序流程图

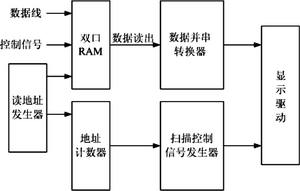

FPGA控制单元软件设计

FPGA控制单元是在QUARTUSII环境下开发的,主要功能是配置双口RAM、传送数据和相应的驱动信号,以实现串行数据的显示。串行数据显示是软件设计的核心,该单元的软件设计模块如图5所示。双端口RAM的配置完全由软件实现,FPGA读双口RAM的A区还是B区是由单片机的HIGHADR引脚控制的。FPGA按照显示驱动的要求读出相应的数据后,还要将这些数据由串转并送至列驱动的74LS595上。扫描控制信号则在数据送到显示驱动的过程中产生,用于实现行、列驱动。

图5 FPGA控制单元软件设计框图

结语

本文提出的基于Cyclone EP1C6和SPCE061A 的LED 大屏幕方案已应用于现场。其基于FPGA的双口RAM 和扫描控制设计使得系统稳定可靠。实践证明,本系统能以多种播出方式显示各种字体和型号的文字和图形信息,与同类设计相比,画面清晰、性能稳定、操作使用简单,具有很好的应用前景。 |

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图