本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

随着数字信号处理器性能的不断提高及其成本与售价的大幅下降,数字信号处理应用领域飞速扩展,信号处理进入了一个新的发展时期。同时随着计算机技术以及互联网络技术的不断发展,越来越多的数据需要经过计算机来进行处理、存储、传输筹操作。计算机的应用已经遍及我们生活的每一个角落。由于计算机本身的特点,通用计算机通常仅负责没有实时性要求的工作,而不适于进行实时性要求很高的数字信号处理。将计算机和 DSP有机地结合起来,充分利用各自的优点,它们将会相得益彰,满足现实应用中对数据实时处理能力、数据传输能力以及数据管理能力提出的越来越高的要求。

PCI总线是先进的高性能32/64位局部总线。可同时支持多组外围设备,不受制于处理器,数据吞吐量大(32位时峰值高达132Mb/s),并能完全兼容现有的ISA/EISA/MAC等扩展总线。连接到PCI总线上的设备主要分为:主控设备和目标(从)设备两类,接口设计成为PCI总线与设备进行沟通的桥梁。但是PCI总线的规范十分复杂,其接口的实现比ISA等总线要困难得多。目前实现PCI接口的有效方案有两种:使用可编程逻辑器件和使用专门接口芯片。本文中的采集系统就是运用TI公司的TMS320C5410高速定点DSP和PLX公司的PCI9052 PCI总线接口芯片来搭建的。

1 系统功能概述

根据实际应用析需要,系统的主要功能有:

(1)可以同时采集处理一条E1链路上所有32个时际的数据;

(2)对数据进行链路层协议解包后,重新打包茂特定的格式,交给上层系统(PC机)保存或进一步处理。对链路数据状态和采集的统计信息进行监测,定时生成报表,交给上层系统实时显示;

(3)系统应具有尽量大的软件升级功能和灵活性,便于系统提高性能或者应用于其他通信业务数据的采集。

本系统的设计难点主要是如何实现DSP与PCI9052之间高效率的数据通信。在系统中PCI9052通过DSP上专门的高速主机通用接口(host port interface,以下简称HPI口)和DSP进行通信。但是HPI口总线是一个非常特殊的总线,它采用访问寄存器的方式来进行DSP内部数据的读写,HPI口单纯映射到PCI的I/O空间或者存储器空间,有不可避免的缺点。本文提出了一种双映射方法,成功地解决了这一问题,实现了DSP与PCI9052之间方便、高速的数据通信。

2 系统的硬件设计

整个硬件系统主要由DSP、PCI总线接口芯片和链路数据采集芯片组成。

本系统采用TI公司的TMS320C5410(以下简称C5410)DSP,该芯片的特点有:

·处理能力可达到100MIPS;

·采用多总线技术,一条指令可以同时访问数据和程序空间,具有高度并行性;

·具有改进型的8位HPI接口,主机通过HPI口可以访问DSP系统的任何一个存储器单元,而且外部访问和DSP内部操作相互独立,互不干扰;

·软件可编程的等待状态发生器,可以灵活地用不同速度的器件组建系统。

数据采集芯片采用了PMC公司的PMC4351.它可以同时采集三个时隙上的数据,可以通过编程选择采集或输出T1、E1数据,支持HDLC协议,可以进行去除CRC标志、复帧标志等预处理,为每小时隙提供128字节的发送FIFO和接收FIFO,有很完善的处理器接口。为了能够同时采集一整条E1链路上的数据,本系统采用了11片PMC4351组成链路数据接口单元。各个芯片之间的接口利用CPLD来完成,它的可编程性为各个组成部分之间的控制和通信提供了相当大的灵活性,也省去了大量外部电路、保证了硬件的方便调试和稳定工作。

具体的硬件框图如图1所示。

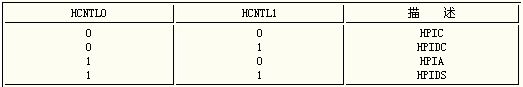

3 DSP的HPI接口与PCI9052的连接

C5410上的增强型8位HPI口为上层系统提供了一个灵活访问DSP内部存储器的并行数据口。上层系统可以通过HPI口自由地读写DSP内部存储器中的任何一个单元。并且C5410为HPI口提供了专门的中断线,这样两个系统可以通过中断进行控制信息交互。HPI为上层系统的访问提供了四个端口,通过这四个端口上层系统可以读写HPI的地址寄存器(HPIA)和控制寄存器(HPIC);通过另外两个端口HPIDC和HPIDS来分别连续和单个读写C5410存储器中的数据。这四个端口由HCNTL0和HCNTL1来寻址,它们的地址分配如表1所示.

表1

本系统采用双映射方式来完成C5410与PCI9052的连接。第一个映射是将HPI口的四个寄存器分别映射到PCI空间的四个16位I/O口上。上层系统可以通过访问I/O端口的方式来访问这四个寄存器,而依照HPI口的工作流程就可以间接地访问C5410内部存储器。这四个寄存器和PCI9052本地I/O空间的对应关系如下:

HPIC--100H

HPIDC--104H

HPIA--108H

HPIDS--10CH

在这种映射方式下,上层系统可通过PCI的I/O访问方式直接访问HPI口的四个寄存器,操作很直观。由于I/O访问无法进行突发传输,从而限制了数据传输速度。

第二种映射方式是将HPIDC寄存器映射成PCI空间的一个长度为2000H的8位存储器块。上层系统对该地址空间内任一单元的读写操作都会被映射成对HPIDC的读写访问。写入的情况也类似。可以看出,实际上这种模式形成了一个PCI存储器空间和DSP内部存储空间之间一一对应的直接映射。

本系统利用I/O映射来访问控制、地址寄存器和单个数据口,并用存储器映射来访问连续数据口。

在这种配置方法下,PCI9052和HPI口之间的硬件连接,主要利用PCI9052的读写控制信号ADS#、LBE[30]#、LW/R#、LRDY#和部分地址信号LA[32]进行简单的时序和逻辑转换后来生成HPI口的读写控制信号HBIL、HDS1#、HCNTL0/1、HR/W#.由于HPI口的访问时钟是C5410的外部频率CLKOUT的5分频,所以PCI9052的本地时钟采用CLKOUT/5.

所有控制信号的接口逻辑和时序转换都是由CPLD来完成,具体的连接方式如图2所示。

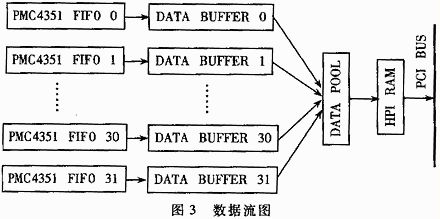

4 系统的软件设计

数据的采集与预处理需要在C5410数据存储器中开辟三种存储块:一种是DATA BUFFER,它与PMC4351中各个时隙的FIFO一一对应,用于缓存每个时隙上采集到的消息数据;第二是DATA POOL(大小为1000H字),这是一个消息数据地,消息数据在DATA BUFFER中存满一整条消息后,加上一些TS包头后,形成一个新的消息包,存入到DATA POOL中;另外还要再开辟一个大小为1000H字节的存储块HPI RAM,这样就将DSP的数据采集部分与上层系统通信部分相互隔离开来,互不干扰。在DATA POOL中存满数据后,形成一个大的数据包,交给HPI RAM,通过PCI总线交给上层系统,进行进一步处理。整体的数据流图如图3所示。

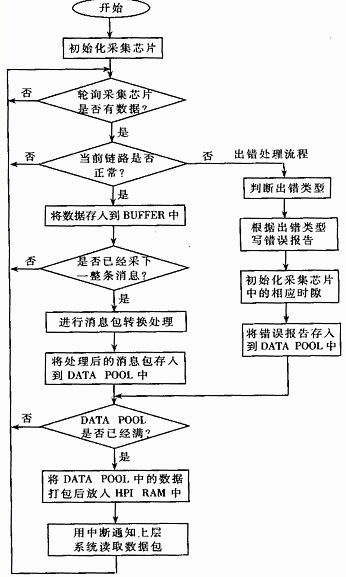

由于DSP芯片的中断引脚数目有限,而且中断工作方式容易造成各个时隙数据采集不均匀的情况,本系统采用了轮询的工作方式。软件的具体流程如图4所示。

图4 软件流程图

本文提出的双映射配置方法和DSP软件工作策略,将C5410 DSP和PCI总线相互连接,接口具有逻辑简单、操作方便、效率高等优点。在C5410的CLOCKOUT配置成64MHz的前提下,两者之间数据传输速率理论峰值可达12.8Mbps,实际系统实现的平均速率达到了10Mbps。采用高性能的采集芯片,可充分发挥HPI口与PCI9052之间的高速数据连接,同时系统也可以升级到同时采集10条E1链路。

本文实现的数据采集系统工作良好,并已经在电信部门得到采用。该系统目前已经不仅仅用于采集移动通信数据,也开始应用于采集V5、七号信号等协议的数据,满足了系统功能设计的要求。 |

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图