本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

1. 引言

随着IP网络的蓬勃发展、新的应用不断涌现,用户对网络带宽的要求也越来越高。运营商采用OC一192(10Gbps)接口的光纤传输大大提高了光传输网络的容量,而路由器作为网络的主要节点设备,其处理速度就成为网络通信的主要瓶颈之一。一台具有50个oc一192接口的路由器交换容量将达到T比特级,国外T比特路由器已经开始试运行,国内开发T比特路由器也迫在眉睫。本文所研制的T比特路由器,系统总吞吐率可达1.28Tbps,峰值交换能力为2.4Tbps,而每端口可达到10G的转发速率;为达到10G的转发速率,本路由器采用了4路2.5GPOS接口。

2. 硬件总体结构设计

本路由器硬件体系结构由线路接口子系统、转发处理子系统、光背板交换网络子系统和内部通信子系统四大部分组成。当接口收到数据包后,首先判断该包的目的地址是否为本路由器,是则上交给单板软件并由内部通信子系统交给主控处理;否则填充内部包头,注明包类型,协议类型,目的机架号,端口号,接口号等信息,由同轴电缆交给转发处理子系统,再由光背板转发到目的接口。接口把转发送过来的包和本路由器发出的包,进行和路处理后再发送出去。

2.1 性能需求分析

1)根据以往路由器的经验,通常硬件FPGA 中的高速通道工作在2.5Gbps速率下比较稳定。就A口输入数据速率10Gbps来说,4个2.5Gbps的高速通道就可以将数据传到转发处理模块。但是,线路接口模块的功能实现要求:数据包在经过线路接口输入处理模块的处理后要加上128 bit即16个byte的内部标签。考虑极限情况,A口收到的都是40 byte的超短包,那么,B口输出的数据的极限速率为:[10Gbps×(40 byte+16 byte)]/40 byte=14Gbps.所以,本设计采用两路2.5Gbps的高速通道来传A口接收的10Gbps数据中的四分之一即2.5Gbps数据到转发处理模块。那么,B口的最大输出速率为2.5Gbps×8=20Gbps,完全满足B口传输带宽要求。

2)在均匀输入业务模型和平衡输出模型条件下,假定定长分组业务强度λ为0.95,为了控制分组的丢失概率小于10-8,可计算所需要的输出队列分组缓冲容量S约为650个分组。统计意义上IP分组的平均长度为508字节。考虑到内部分组标签附加的24字节,平均需要缓冲的IP分组字节数为532字节 总缓冲容量为650×532×8=2766400(Bits),即近似为2.8MBits。

3)本子系统的接口速度要达到10Gbps,如果每个包都是40字节,那么这时极限查表速率为:

对于输入查表模块的另一个指标为表项容量。按照极限容量来算,T比特路由器有8个机架,每个机架8个端口,每个端口8个接口,每个接口的IPv4单播组播、IPv6单播组播地址总计有64个。那么极限表项容量为8*8*8*64=32768(32k)条。达到这两个设计指标是本模块设计的一个难点。最终,我们选择了一款CAM,有64K条表项,查表速率能够达到100MSPS.这样的指标完全可以达到本模块的要求。

2.2 子系统功能划分和模块设计

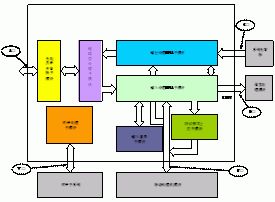

如下图所示,4 2.5G线路接口子系统可划分为光电及串并转换模块、链路层处理模块、输出FPGA处理模块、输入FPGA处理模块、协议报文上交缓存模块、输入查表模块和时钟处理模块。为描述方便,将本子系统和路由器外部的接口称为A口,和转发处理子系统的接口称为B口,和光背板子系统的接口称为G口,和单板处理机的接口称为F口,和时钟子系统的接口称为J口。

从路由器外部接收数据时,光电及串并转换模块负责从A口接收4路2.5Gbit/s串行光信号,转换成16路差分622Mhz电信号;送由链路层处理模块进行链路层处理。输入FPGA处理模块针对输入包的类型,对输入查表模块存储的本机IP地址表查表,进行分路处理,若此报文的目的为本路由器则上交主控,否则转发到B口。输出FPGA处理模块负责接收主控下发协议包和从系统光背板转发G口数据包,合路后交给链路层处理模块。链路层处理模块把和路后的ppp报文封装在SDH帧中,由光电及串并转换模块转换成光信号发送出去。时钟处理模块为本模块提供全局时钟和将本模块从线路上提取的时钟输出到时钟板。

3. 软件总体结构设计与实现

MPC860是基于PowerPC结构的通信控制器。MPC860具有存储控制器,其存储控制器的功能很强,可以支持各种存储器,包括各种新型的DRAM和Flash,并可以实现与存储器的无缝接口。

VxWorks是一套具有微内核,高性能,可伸缩的操作系统,支持广泛的网络通信协议,并能够根据用户的需求组合,增减。再加上其优秀的开发环境Tornado,使其成了嵌入式操作系统的首选。选择MPC860加上嵌入式强实时操作系统VxWorks完全可以买足单板处理的性能需求。

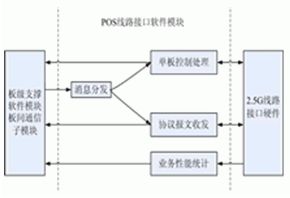

上图展示了单板软件总体结构。单板操作系统是采用VxWorks,单板处理器是采用MPC860.路由器有不同种类的线路接口板,每种接口板都需要完成许多相同的功能,可把这些相同的功能放在一个单独的模块中实现,减少冗余劳动。板级支撑模块为单板应用提供与主控软件之间的通信、任务管理、内存管理和定时器管理等服务;而单板应用为线路接口单板软件模块,完成单板转发处理。

单板软件主要完成的功能有:对各类型单板硬件的初始化和配置,接收并处理主控下发的单板控制命令,完成软硬件程序加载,以太网接口板运行IPv4 ARP协议,维护并向主控通告ARP信息,协议数据(源/目地址为本路由器的分组)收发,维护路由器接口地址信息,差错报文处理、记录报文上报,业务性能统计数据收集与上报,维护单板与主控板间的通信连接。

其数据处理流程如下图:单板硬件接收到本路由器包,写入输入FIFO,收包任务读出包,封装在定义的内部数据结构中,调用板级支撑模块中的发送函数发给主控;主控下发的包则由消息分发模块处理,协议包交给发包任务,再写入输出FIFO,然后发送出去,控制包则交主控处理模块处理,完成向对应的功能。

由于本接口需要达到10G的速率,各任务之间必须有稳定和高速交互机制。VxWorks操作系统为任务间通信提供了许多通信方式,包括共享内存,信号量,消息队列和管道,Sockets和远程调用等。消息队列允许长度可变,数目可变的消息队列,可以满足多任务之间通信。而对相同优先级的任务必须预先设置各任务的执行时间,否则第一个获得CPU 的任务就会独占,阻碍别的人物运行。总之,在软件设计中一定要充分了解VxWorks的工作机制,否则不但不能设计出效益高的程序,反而会阻碍VxWorks的有效运行。

4. 结束语

路由器作为Internet 的核心设备,对于Internet 的性能有着重要影响。历史上,路由器体系结构的变迁体现了由通用器件向专用器件,由串行处理向并行处理,从集中式到分布式的趋势。依此可将路由器体系结构划分为4代:单处理器集中式总线结构,多处理器分布式共享总线结构,多处理器分布式交换结构,多机互连的可扩展集群结构。第一代路由器中,单一的中央处理器和总线成为系统计算能力和通信能力的瓶颈。第二代~第四代路由器体系结构逐步解决了这方面的问题:第二代体系结构提高了线卡的报文转发能力,主要贡献为将中央处理器从报文转发中解放出来;第三代体系结构中采用了交换结构代替总线,通过构造"无阻塞"的交换网络来大幅度提高交换性能;第四代体系结构目前仍在不断发展的过程中,通过某种互连方式将多个路由节点有机地结合在一起的可扩展路由器体系结构将是充满希望的发展方向。

本文简要介绍了吞吐率高达1.28T比特的高性能路由器,并研究了其2.5GPOS接口的实现技术,首先可以深入对POS技术在实现和应用上的研究,其次可以丰富路由器的接口功能,增加路由器接口的灵活性,增强路由器的兼容性,以便更为广泛的利用网络资源,实现网络体系和架构的演进,为高性能路由器的研制和后续开发提供可借鉴的技术思路。 |

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图