本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

高速串口数据通信在现代通信系统和控制系统中应用日益广泛,较之传统的基于RS232传输标准,具有更高的可靠性,更强的兼容性,更快的传输速率。

由于不同的串口数据通信采用的方式各不相同,有异步模式、同步模式,而且数据传输格式也各不相同,有的采用传统SCI传输格式,有的采用自定义数据格式,有的采用帧长度固定方式,有的采用帧长度可变方式等,而且每一帧的数据长度可以从10bit到几千bit,所以高速串口的设计要求不同其实现方案也不同。本文重点介绍基于SOPC(可编程系统芯片)的高速异步串口通信系统的设计方法。

目前的嵌入式处理器种类繁多。Altera 公司的Nios II处理器是用于可编程逻辑器件的可配置的软核处理器,与Altera 的FPGA 组合,具有很高的性价比。

总体设计及系统架构

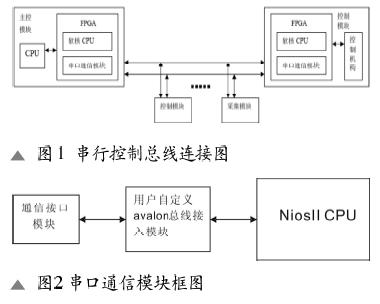

高速串口数据通信系统采用双线平衡驱动,半双工同步传输或单向广播同步传输,线路传输速率为5Mbits/s,总线连接关系如图1所示。

系统中主机模块能调度总线上的数据帧收发,保持数据通信的实时性,数据传输时由主机模块发送数据帧。数据帧若为半双工同步传输帧,则数据帧只对其中一个外围模块有效,同时当外围模块收到数据后,应发送相应的应答信号;数据帧若为单向广播同步传输帧,则数据发向所有外围模块,而不需要任何应答信号。

系统以固定的数据帧格式传送数据,不同于传统的SCI格式,帧长为7字节(共56bits),由2字节引导序列、1字节地址,3字节数据、1字节帧结束序列组成。帧的发送顺序:字节内低位先发,多字节内低字节先发。

无论是主机模块还是外围模块均采用相同的串口通信设计,串口通信设计包含两个主要部分:通信接口部分和管理控制部分。通信接口部分主要完成数据帧结构的封装和解封装,并通过帧头的分析识别进行时隙定位,同时能让系统内的每一终端实现多机共享通信资源的通信机制,该模块由VHDL语言实现。管理控制部分由NiosII软核实现的,为了能在串行通信方式上实现时分复用,进而实现多设备同时通信,系统设计出一套完整而独特的控制帧格式,并通过这些帧格式控制实现建立连接,撤销连接和相应管理。因此,利用NiosII的特点,形成特殊的帧头判决、同步时钟提取、控制信息的判断、收发模式变换,这些都依赖专用模块的实施并靠高速执行速度来适应多终端下的高传输速率。

鉴于以上系统架构和设计要求,串口通信采用模块化设计思路和方法,模块结构如图2所示。

NiosII软核CPU开发工具SOPC Builder提供简洁的操作方式,可将用户的数字电路模块封装成标准的NiosII软核外设模块,这使得NiosII软核可以很容易地与用户逻辑结合,构成功能更加强大的SOC系统。在高速串口数据通信的设计中,既需要一个高速的处理器作为系统的控制管理核心,又有大量用户自定义的数字电路功能模块需要在FPGA芯片中实现,因此,采用FPGA芯片和NiosII软核CPU作为高速串口数据通信的硬件平台是一个优化的选择。

通信接口模块设计

通信接口模块设计采用VHDL语言设计,由两部分组成:数据帧发送电路和数据帧接收电路。数据帧发送电路将NiosII 要发送的数据、地址按照数据帧格式进行组帧,然后同步传输到总线上,该部分设计的关键是并串转换、合并数据和同步控制,数据的发送率为5Mbits/s,而工作时钟fclk为25MHz,对fclk进行5分频,得发送时钟ftxd为5MHz。当有数据要发送时,每一个即ftxd的上升沿到来时传送数据,先发送帧头2字节引导序列,即“1110011100111110”,然后发送串行数据。由于NiosII的内部数据宽度通常是32位,故将1字节地址和3字节数据由软件将其合并成一组32位宽度的数据,合并时地址在低位,数据在高位,然后将要发送的32位数据缓存在一个32位宽度的矢量区间,引导序列结束后从低位到高位依次发送数据,即data[0]、data[1]……data[],最后发送结束标志字节“1110011”,发送结束。

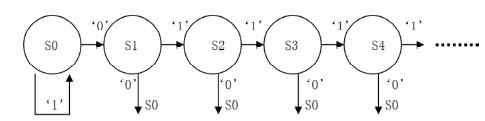

接收电路的设计重点考虑的问题是如何准确判断到数据帧头,然后解析地址,数据的速率为5Mbit/s,FPGA的工作时钟fclk为25MHz,参考RS-232串口通信的设计思想,用高倍时钟对接收的数据进行采样,即每5个fclk采样一个bit,此处可以先设计一个5进制计数器,每一次计数,保存采集的数据,在第2、3、4次采样时,若所采到的值相同,则判断这个bit为当前的采样值。在判断2字节引导序列时采用状态机设计法和序列检测器的设计思想,判断第1个bit是否为‘0’,如果是‘0’则继续判断下一bit是否为‘1’,如果是‘1’则一直等待在第1状态直到判断到‘0’才跳转,判断状态机如图3所示。

用户定义的Avalon总线模块设计

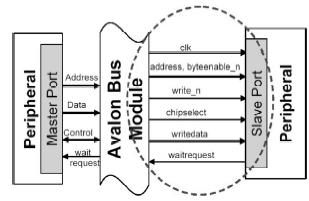

NiosII是基于RISC技术的通用嵌入式处理器芯片软内核,它特别为可编程逻辑进行了优化设计,也为可编程单芯片系统设计了一套综合解决方案。Avalon总线是一种高效的总线结构,主要用于连接片内处理器NiosII和各种外设IP core,以构成可编程系统芯片(SOPC)。数据帧发送电路和数据帧接收电路通过Avalon总线和NiosII处理器连接在一起,Avalon总线规范定义了主端口和从端口之间通过Avalon总线模块传输数据所需的信号和时序。设计时通信模块采用从端口传输模式,数据帧发送电路采用具有外设控制等待周期的从端口写传输模式,发送电路除串行数据输出线外,还必须提供符合Avalon总线传输要求的信号线,即Address、Writedata(31..0)、Write_n、Chipselect、Waitrequest,与NiosII工作同步的时钟信号clk,当CPU要发送数据时,将Address、Write_n信号有效,同时将要发送的32位数据装载到Writedata(31..0)上,而同步时钟clk一直处于工作状态,当clk上升沿判断到以上信号有效后,Avalon总线对Address译码,然后置Chipselect有效,而发送电路VHDL程序设计时必须判断Address、Chipselect是否有效,如果有效,则在下一个clk上升沿前将Waitrequest置为无效,数据传送电路就从Avalon总线获取Writedata数据,如果Waitrequest有效,则这个总线周期就成为等待周期,其他信号以及数据信号保持不变,但外设必须保证不会使Waitrequest无限期地保持有效,这样会使得一个从外设能够将Avalon总线永久“挂起”,其连接关系和时序关系如图4所示。同理,数据接收电路采用具有外设控制等待周期的从端口读传输模式,可以将串转并后的数据送入到NiosII中进行处理。

软件设计

基于NiosII的C语言设计,可以采用单线程模式,也可采用uc/基于NiosII的C语言设计,可以采用单线程模式,也可采用uc/OSII多任务操作系统。这里对接收和发送的数据处理主要采用以下指令实现,“IORD(base, 1)”读指令,其中base就是需要读取的外设基地址,数据接收电路作为外设在建立SOPC Builder时定义的名称为“user_uart_rxd”,则base应改为“user_uart_rxd_base”,而第2个参数‘1’表示其偏移地址;“IOWR(base, 1, data)”写指令,其中base是需写入外设基地址,数据发送电路作为外设在建立SOPC Builder时定义的名称为“user_uart_txd”, 则base应改为“user_uart_txd_base”,而第2个参数‘1’表示其偏移地址,第3个参数data是发送数据。

计算机仿真波形如图5、图6所示。它们之间的时序关系参照本文的第二部分。

结语

运用此5Mbit/s的UART进行通信,效果十分稳定、可靠性高,传输速度快,采用RS485接口模式传输距离远,同时不易被干扰以至出现误码、丢数据、丢帧等情况。因此采用SOPC嵌入式系统设计技术可以实现系统设计的小型化、集成化和高可靠性,还可以减少风险、降低成本、缩短开发周 |

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图