本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

1. 引言

对于需要大的片上存储器的各种不同的应用,FPGA 需要提供可重构且可串联的存储器阵列。通过不同的配置选择,嵌入式存储器阵列可以被合并从而达到位宽或字深的扩展并且可以作为单端口,双端口存储器,只读存储器,FIFO,大的查找表或移位寄存器,每种应用都支持不同的数据宽度和高度。

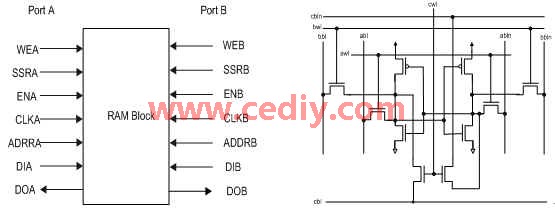

在本文中我们设计的嵌入式存储器是一个可配置的同步16Kb模块。如图1所示,每个存储器模块有两个独立的端口,它们的结构和工作模式完全对称,并且支持双端口工作模式。每个端口都有自己的时钟信号,时钟使能信号,写信号。虽然对每个端口的操作是完全同步且独立于另一个端口的,但是可以通过外面的电路连接扩展数据位宽或地址宽度。当写允许信号WEN为低,EN为高时,存储器模块读取地址确定的存储单元的数据,当WEN和EN同时为高时,输入总线上的数据被写入存储单元。在存储器模块被用于流水线逻辑中的情况下,根据数据路径逻辑获取存储器数据时不同的需要,每个存储器模块的写数据过程可以配置成三种工作模式。根据不同的配置,输出数据总线上的数据可以随输入数据同时更新,或者一个时钟周期后更新,或者保持不变。

每个存储器模块都支持多种配置方式,可以配置成以下各种工作模式:16Kx1, 8Kx2, 4Kx4, 2Kx8, 1Kx16 and 512x32。一个可重构的正交开关矩阵用于连接输入/输出与外部数据总线。存储器模块可以配置成只读存储器。只读存储器的数据在配置过程通过第三个端口确定,也即下面讲到的存储单元的C端口。在配置过程,该配置端口支持读写操作。

一种全新的存储单元的设计方法以及实现各种配置的电路设计方法将会重点介绍。最后将给出Nanosim的仿真结果。

图1. 存储器模块 图2 三端口存储单元

2. 存储器模块的设计

2.1 存储单元的设计

当存储器模块配置为只读存储器时,只读存储器的内容必须要在FPGA的配置过程予以定义,在有些情况下还需要对存储器模块的内容予以初始化,所以存储单元需要提供一个端口专门用于存储器内容的定义或初始化。我们的存储单元采用的是一个三端口的结构,其中两个端口用于片上逻辑,第三个端口用于片外逻辑。片外即第三个端口用于只读存储器或查找表的内容定义或静态存储器的内容初始化,也可用于存储器测试中的验证。如图2所示,存储单元实际上是一对交叉耦合的反相器,通过三对NMOS与三个端的位线(bitline)连接,三个端的字线分别控制各端的NMOS导通与否。A,B端用于片上逻辑的读写操作,而C端作为配置端只在配置过程中应用。A,B两端口的位线为垂直走向,字线为水平走向,而配置端C端恰好相反,其位线为水平走向,字线为垂直走向,原因在于在FPGA的配置过程中 ,配置数据按列送入FPGA[4][5]。这种存储器单元结构同时满足了实现存储器模块的片外配置功能和片上功能的需要。

2.2 位线结构

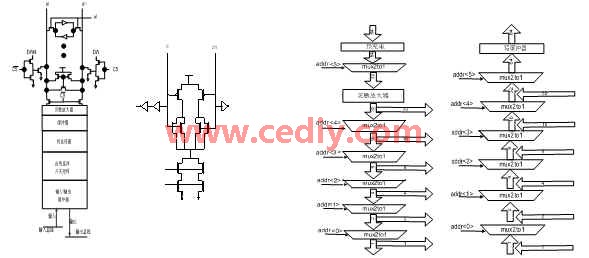

A,B两端口的位线结构用于正常的读写操作,下图3给出了此位线结构。一列存储单元(256个)共用一对位线,它们在读/写过程的开始前被预充电至vdd,然后被选中的存储单元驱动(读过程)或被输入缓冲器驱动(写过程)。在读过程中灵敏放大器被其使能信号触发以放大位线上的差分信号,然后其单输出数据经过缓冲器被驱动经过列选择器,再经过总线选择开关矩阵,最后到达输出数据总线。灵敏放大器用于将小信号的差分输入(位线电压)放大为大信号的单端输出。如图3.B所示我们采用了一种锁存型灵敏放大器,它的两个输出经过一个改进缓冲器以单端输出,这种灵敏放大器结构简单,驱动能力强,建立时间短,有效地缩短了存储器的读取时间,提高了性能[1],[2]。

2.3 配置电路的设计

如前所述,存储器模块可以配置成以下存储器结构:16Kx1, 8Kx2, 4Kx4, 2Kx8, 1Kx16 以及512x32,配置电路就是能够实现这些配置的逻辑。组成配置电路的就是上面提到的列选择器和总线选择开关矩阵。通过对列选择器和总线选择开关矩阵的配置,可以实现以上各种存储器结构,以及读过程中的三种输出模式。

存储器模块的存储单元阵列采用的是256x64的结构,即每列为256个存储单元,每行为64个存储单元。读操作过程中,由于我们能够实现的最大位宽的存储器结构为512x32,所以在预充电电路与灵敏放大器之间我们加入了一个2选1的选择器,这样进入灵敏放大器的位线有32对,32个灵敏放大器是必需的。 32位数据从灵敏放大器输出后就进入输出列选择器,如图5(a)所示,我们用到了五个二选一的选择器,各由一位地址选择,同时其工作状态由配置信息控制,各选择器的输出按照配置信息或者提供相应结构的数据或者被置为高阻态。被选出的数据经过输出总线选择开关矩阵,最后到达数据总线。在写操作过程中,数据总线上的输入数据首先进入输入总线选择开关矩阵(与输出总线选择开关矩阵相似),然后进入输入列选择器(与输出列选择器相似,图5(b)所示),输入列选择器的输出经过缓冲器后(图3.a中DW, DWN)被直接写入选中的存储单元。

图 3. 位线结 (a) 读列选择器 (b) 写列选择器 图4 .读/写列选择器

2.4 存储器模块的体系结构

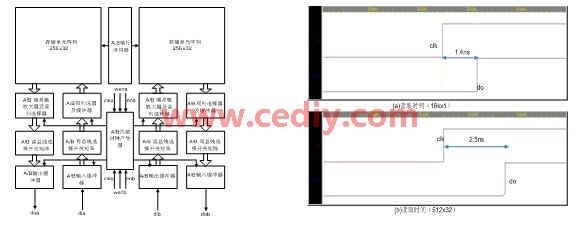

图5给出了存储器模块的总体结构[3]。每个存储器模块的存储单元阵列被分为两部分,分别为256x32,即每列256个存储单元,每行32个存储单元[6],[7]。A,B两端口分别拥有独自的行译码器,预充电电路,灵敏放大器,输入/输出列选择器,输入/输出总线选择开关矩阵,时钟产生器以及输入输出缓冲电路。预充电电路用于在读操作前将耦合位线预充至某一相同电压值。行译码器采用两级译码,从而提高读写操作速度。时钟产生器用来产生内部时钟以控制译码器,灵敏放大器,多路选择器,预充电电路以及输入输出寄存器[3]。

3. 读写操作仿真结果

关键路径我们选择位于位线结构顶端的存储单元,对该存储单元的读写操作反映了最坏情况下的延时[4]。由于存储器模块可以配置为不同的结构,所以各种结构的关键路径长度并不相等,显然512x32这种结构中数据经过最少的选择器,所以关键路径最短,而16kx1结构的关键路径最长,因为数据要经过最多的选择器。我们对这两种关键路径做了重点仿真,这也足以反应存储器模块的性能。

我们用Synoposys的工具Nanosim针对各种读写操作基于0.13微米CMOS工艺做了详细的仿真。图7给出了512x32 和16Kx1这两种工作模式下的关键路径上的读取时间。时钟上升沿到数据读出有效之间的延时分别是1.4ns和2.5ns,读取时间不同的原因在于对于不同的工作模式数据经过的关键路径的长短不同,512x32模式下经过的关键路径最短,而16Kx1模式下关键路径最长,所以这两种模式之间的各种模式下的读取时间在1.4ns和2.5ns之间。

图 6. 存储器模块体系结构 图 7.存储器读取操作的仿真结果

4. 结论

本文介绍了基于0.13微米CMOS工艺下平台式FPGA中可重构RAM模块的一种设计方法。该RAM模块是一个16Kb的高速低功耗可重构模块,通过不同的配置信息,可以实现多种功能。重点介绍了一种用于可重构静态存储器的全新的存储器单元电路结构以及实现该静态存储器各种重构功能的电路结构。仿真结果表明我们设计的该存储器模块能够很好的实现各种重构功能,而且速度高,功耗较低。

本文作者创新观点:本文所设计的存储器采用了一种新颖的三端口存储单元,同时在外围电路采用了可配置的列选择器,从而可以通过不同的配置信息把存储器配置到多种工作模式,该存储器具备了良好的可重构性能。 |

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图