本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

1.引言

随着集成电路技术的发展, 在现代电子设计中,可编程逻辑器件的运用越来越多,原因在于其规模大,体积小,功能强,价格便宜。CPLD可擦写上万次,使得硬件设计像软件设计一样灵活方便。Verilog HDL语言作为硬件描述语言有其独特的优势:在门级描述的底层,描述的设计思想、电路结构和逻辑关系清晰明了,设计语言简练、易学易用,模块化分层结构在大规模设计时具有优势。如果使用Verilog把控制功能集成在一片CPLD芯片里,整个电路将会变得更简洁、实用。

2.液晶控制器原理

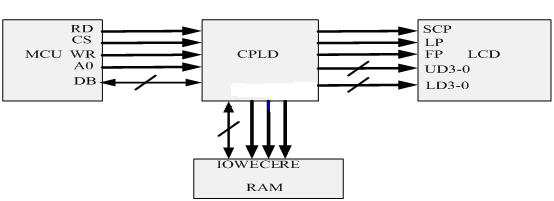

液晶控制器用于单片机和液晶屏的接口,一方面不断地把显存的数据刷新到液晶屏上,另一方面控制单片机对显存数据的更新。

双屏结构液晶控制器内部主要的计数器,分别是4bit时钟同步字符计数器、行计数器和帧计数器,它们在系统时钟FCLK的控制下同时计数,主要是用来产生行同步信号LP 和帧同步信号FP ,分别用来控制液晶屏换行和换页。液晶屏就是在这三个信号的控制下反复地把显存里的数据刷新到屏幕上。

本设计采用Altera 公司生产的EPM7128SCPLD芯片来实现LCD 控制器以及它的外围

逻辑时序的全部功能,使用的液晶屏为640×480双屏显示结构,即上半屏和下半屏同时显示,RAM为一片SRM20512LLTM78(62512)。

液晶屏刷新速度的计算公式为FFRP = FCLK/ ( Hn×Nx )。

其中,FFRP为液晶屏显示帧扫描频率,一般要大于70 Hz ,Hn为一行显示的4bit同步字符数640/4=160,Nx为一屏帧扫描的行数480/2=240,FCLK为系统的工作时钟频率,采用晶振提供频率11.05926MHz,将其四分频得到2.764815MHz即可作为系统时钟FCLK。

系统构成如下图所示:

3.实现过程

1)液晶刷新时序产生

此部分主要产生行同步和帧同步信号,完成行和帧同步。

由于双屏结构液晶屏以4bit为单位上下同时显示,可以在CPLD内定义两个寄存器,行含4bit字符寄存器scp_reg,值为640/4=160, 帧含行寄存器lp_reg,值为480/2=240。字符时钟同步计数器scp_count为4bit字符的计数器,在系统时钟scp_clk作用下计数加一,与行含字符寄存器内容比较,若等,表示一行结束,开始下一行,scp_count清零,行计数器lp_count加一,lp_flag置一,产生行同步信号LP。行计数器lp_count与帧含行寄存器内容比较,若等,表示一帧结束,开始下一帧,scp_count, lp_count 清零,fp_flag置一,产生帧同步信号FP。实现的程序如下:

always@(posedge scp_clk)

begin

scp_count=scp_count+1;

if(scp_count==scp_reg)

begin

lp_count=lp_count+1;

lp_flag=1;

scp_count=0;

if(lp_count==lp_reg)

begin

fp_flag=1;

lp_count=0;

scp_count=0;

end

else fp_flag=0;

end

else lp_flag=0;

end

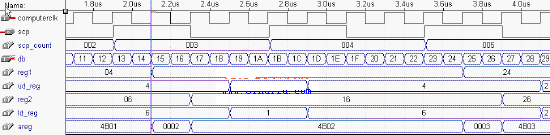

操作lcd时,scp_reg=160,lp_reg=240。仿真时取scp_reg=3,lp_reg=4,如下:

2) 单片机写数据至RAM

此部分为单片机通过CPLD更新RAM数据。

单片机写信号WR有效,CPLD判断数据线上内容为指令还是数据,若为指令,则将DB内容存入指令寄存器CMDREG,若为数据,判断指令寄存器CMDREG内容以指示状态。若CMDREG为8’h00或8’h02,表示DB为低或高八位地址,分别存入低高八位地址寄存器addl和addh,若为8’h04,表示DB为要写入RAM的数据,存入数据寄存器ioreg。

CMDREG DB内容

8’h00 低八位地址

8’h02 高八位地址

8’h04 数据

if(a0==1) cmdreg="db";

else begin

if(cmdreg==8'h00) addl="db";

&nb

sp; else if(cmdreg==8'h02)

begin

addh="db";

p={addh,addl};

end

else if(cmdreg==8'h04) ioreg="db";

end

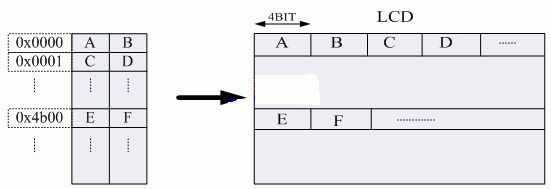

3)显存的数据刷新到液晶屏

此部分完成RAM数据到LCD的正确映射。

RAM存储和LCD对应关系如下图所示:

正确的将RAM中的数据送入LCD,使液晶屏上下半屏随着时钟同时显示,必须理清RAM存储和LCD显示间的地址关系。LCD为640×480,所以下半屏起始地址对应的内容应为640×240/8=19200,即RAM0x4b00中的内容。

由于4bit字符同步时钟scp_clk内含四个周期computerclk,可以在computerclk的二三周期,分别将RAM地址0x0000的内容AB和0x4b00的内容EF传至八位寄存器reg1和reg2,在余下的第四周期,将reg1和reg2的高四位即A和E传至上下半屏数据寄存器ud_reg和ld_reg,lcd将同时显示上半屏A下半屏E。下一个scp_clk时,只需将reg1和reg2的低四位即B和F传至ud_reg和ld_reg,则lcd将同时显示上半屏B下半屏F。以后每两个scp_clk,RAM地址加一,同样的方式取数据刷新lcd。

仿真图中蓝线指示为RAM地址加一后上述一个循环的开始。

4) 数据选择器

单片机对RAM数据的更新,CPLD刷新LCD对RAM的读取,可以通过一个二选一数据选择器完成。

当单片机写时,置选择信号sel为1,存放MCU操作的地址寄存器addl、addh和数据寄存器ioreg与RAM地址数据总线连接,完成MCU对RAM数据的更新;当sel为0,刷新液晶屏的地址寄存器q和数据寄存器ud_reg、ld_reg与RAM地址数据总线连接,刷新LCD。

4.结束语

以上主要介绍了Verilog HDL设计CPLD作为液晶控制器的几个基本部分,经过验证,所设计控制器在单片机作用下正确完成液晶的显示。本设计创新点在于控制器设计使用硬件描述语言Verilog而非传统设计方法设计,易于理解,易于维护,调试电路速度快,有许多易于掌握的仿真综合布局布线工具。若使用其他液晶屏,只需修改程序中相关参数,更多功能的扩充,也只需增添CPLD中的模块即可实现。 |

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图