本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

module i2c (clk, rst, scl, sda, write, read,ack_led, led);

input clk, rst, write, read;

output scl;

inout sda;

output [3:0]ack_led;

output [7:0]led;

reg [7:0] led;

reg [3:0] ack_led;

reg sda;

reg ack;

reg [7:0] current_state;

reg [7:0] next_state;

reg scl;

reg j;

integer counter;

always @(posedge clk)

begin

if(j==1)

begin

j = 0;

scl = 1;

end

else

begin

j = 1;

scl = 0;

end

end

parameter Idle = 8'd0,

I1 = 8'd1, I2 = 8'd2, I3 = 8'd3, I4 = 8'd4, I5 = 8'd5,

I6 = 8'd6, I7 = 8'd7, I8 = 8'd8, I9 = 8'd9, I10 = 8'd10,

I11 = 8'd11, I12 = 8'd12, I13 = 8'd13, I14 = 8'd14, I15 = 8'd15,

I16 = 8'd16, I17 = 8'd17, I18 = 8'd18, I19 = 8'd19,

ack1 = 8'd20, ack2 = 8'd200,

add1 = 8'd21, add2 = 8'd22, add3 = 8'd23, add4 = 8'd24, add5 = 8'd25,

add6 = 8'd26, add7 = 8'd27, add8 = 8'd28, add9 = 8'd29, add10 = 8'd30,

add11 = 8'd31, add12 = 8'd32, add13 = 8'd33, add14 = 8'd34, add15 = 8'd35,

add16 = 8'd36,

ack3 = 8'd37, ack4 = 8'd38,

data1 = 8'd41, data2 = 8'd42, data3 = 8'd43, data4 = 8'd44, data5 = 8'd45,

data6 = 8'd46, data7 = 8'd47, data8 = 8'd48, data9 = 8'd49, data10 = 8'd50,

data11 = 8'd51, data12 = 8'd52, data13 = 8'd53, data14 = 8'd54, data15 = 8'd55,

data16 = 8'd56,

ack5 = 8'd57, ack6 = 8'd58, stop1 = 8'd59, stop2 = 8'd60,

r1 = 8'd61, r2 = 8'd62, r3 = 8'd63, r4 = 8'd64, r5 = 8'd65,

r6 = 8'd66, r7 = 8'd67, r8 = 8'd68, r9 = 8'd69, r10 = 8'd70,

r11 = 8'd71, r12 = 8'd72, r13 = 8'd73, r14 = 8'd74, r15 = 8'd75,

r16 = 8'd76,

start3 = 8'd77,start4 = 8'd78,

add21 = 8'd81, add22 = 8'd82, add23 = 8'd83, add24 = 8'd84, add25 = 8'd85,

add26 = 8'd86, add27 = 8'd87, add28 = 8'd88, add29 = 8'd89, add30 = 8'd90,

add31 = 8'd91, add32 = 8'd92, add33 = 8'd93, add34 = 8'd94, add35 = 8'd95,

add36 = 8'd96,

ack7 = 8'd97, ack8 = 8'd98, ack9 = 8'd99 ,ack10 = 8'd100,

stop3 = 8'd101, stop4 = 8'd102;

always @ (negedge clk) //异步复位

if(rst)

current_state <= Idle;

else

current_state <= next_state;

always @(current_state or write or read)

begin

next_state = Idle;

case(current_state)

Idle:

begin

if(write || read)

next_state = I1;

else

next_state = Idle;

end

I1:

next_state = I2;

I2:

next_state = I3;

I3:

next_state = I4;

I4:

next_state = I5;

I5:

next_state = I6;

I6:

next_state = I7;

I7:

next_state = I8;

I8:

next_state = I9;

I9:

next_state = I10;

I10:

next_state = I11;

I11:

next_state = I12;

I12:

next_state = I13;

I13:

next_state = I14;

I14:

next_state = I15;

I15:

next_state = I16;

I16:

next_state = I17;

I17:

next_state = ack1;

ack1:

next_state = ack2;

ack2:

next_state = add1;

add1:

next_state = add2;

add2:

next_state = add3;

add3:

next_state = add4;

add4:

next_state = add5;

add5:

next_state = add6;

add6:

next_state = add7;

add7:

next_state = add8;

add8:

next_state = add9;

add9:

next_state = add10;

add10:

next_state = add11;

add11:

next_state = add12;

add12:

next_state = add13;

add13:

next_state = add14;

add14:

next_state = add15;

add15:

next_state = add16;

add16:

next_state = ack3;

ack3:

next_state = ack4;

ack4:

if(read) next_state = start3;

else next_state = data1;

data1:

next_state = data2;

data2:

next_state = data3;

data3:

next_state = data4;

data4:

next_state = data5;

data5:

next_state = data6;

data6:

next_state = data7;

data7:

next_state = data8;

data8:

next_state = data9;

data9:

next_state = data10;

data10:

next_state = data11;

data11:

next_state = data12;

data12:

next_state = data13;

data13:

next_state = data14;

data14:

next_state = data15;

data15:

next_state = data16;

data16:

next_state = ack5;

ack5:

next_state = ack6;

ack6:

next_state = stop1;

stop1:

next_state = stop2;

stop2:

next_state = Idle;

start3:

next_state = start4;

start4:

next_state = add21;

add21:

next_state = add22;//第二次送地址

add22:

next_state = add23;

add23:

next_state = add24;

add24:

next_state = add25;

add25:

next_state = add26;

add26:

next_state = add27;

add27:

next_state = add28;

add28:

next_state = add29;

add29:

next_state = add30;

add30:

next_state = add31;

add31:

next_state = add32;

add32:

next_state = add33;

add33:

next_state = add34;

add34:

next_state = add35;

add35:

next_state = add36;

add36:

next_state = ack7;

ack7:

next_state = ack8;

ack8:

next_state = r1;

r1:

next_state = r2;

r2:

next_state = r3;

r3:

next_state = r4;

r4:

next_state = r5;

r5:

next_state = r6;

r6:

next_state = r7;

r7:

next_state = r8;

r8:

next_state = r9;

r9:

next_state = r10;

r10:

next_state = r11;

r11:

next_state = r12;

r12:

next_state = r13;

r13:

next_state = r14;

r14:

next_state = r15;

r15:

next_state = r16;

r16:

next_state = ack9;

ack9:

next_state = ack10;

ack10:

next_state = stop3;

stop3:

next_state = stop4;

stop4:

next_state = Idle;

default:

next_state = Idle;

endcase

end

always @ (negedge clk)

begin

case(next_state)

Idle:

begin

sda <= 1;

end

I1:

sda = 0; //start bit

I2:

sda <= 1; //1//地址1010 000 0 写初始化 两个周期一个数据

I3:

sda <= 1;

I4:

sda <= 0;//0

I5:

sda <= 0;

I6:

sda <= 1;//1

I7:

sda <= 1;

I8:

sda <= 0;//0

I9:

sda <= 0;

I10:

sda <= 0;//0

I11:

sda <= 0;

I12:

sda <= 0;//0

I13:

sda <= 0;

I14:

sda <= 0;//0

I15:

sda <= 0;

I16:

sda <= 0;//0

I17:

sda <= 0;

ack1:

sda <= 1'bz;

ack2:

begin

ack_led[0] <= ~sda;

sda <= 1'bz;

end

add1:

sda <= 0; //add 0000 0001

add2:

sda <= 0;

add3:

sda <= 0;

add4:

sda <= 0;

add5:

sda <= 0;

add6:

sda <= 0;

add7:

sda <= 0;

add8:

sda <= 0;

add9:

sda <= 0;

add10:

sda <= 0;

add11:

sda <= 0;

add12:

sda <= 0;

add13:

sda <= 0;

add14:

sda <= 0;

add15:

sda <= 1;

add16:

sda <= 1;

ack3:

sda <= 1'bz;

ack4:

begin

ack_led[1] <= ~sda;

sda <= 1'bz;

end

data1:

sda <= 1;

data2:

sda <= 1;

data3:

sda <= 0;

data4:

sda <= 0;

data5:

sda <= 1;

data6:

sda <= 1;

data7:

sda <= 0;

data8:

sda <= 0;

data9:

sda <= 1;

data10:

sda <= 1;

data11:

sda <= 0;

data12:

sda <= 0;

data13:

sda <= 1;

data14:

sda <= 1;

data15:

sda <= 0;

data16:

sda <= 0;

ack5:

sda <= 1'bz;

ack6:

begin

ack_led[2] <= ~sda;

sda <= 1'bz;

end

stop1:

sda <= 0;

stop2:

sda <= 1;

//读数据

start3:

sda <= 1;

start4:

sda <= 0;

add21: //1010 0001

sda <= 1;

add22:

sda <= 1;

add23:

sda <= 0;

add24:

sda <= 0;

add25:

sda <= 1;

add26:

sda <= 1;

add27:

sda <= 0;

add28:

sda <= 0;

add29:

sda <= 0;

add30:

sda <= 0;

add31:

sda <= 0;

add32:

sda <= 0;

add33:

sda <= 0;

add34:

sda <= 0;

add35:

sda <= 1;

add36:

sda <= 1;

ack7:

sda <= 1'bz;

ack8:

begin

ack_led[3] <= ~sda;

sda <= 1'bz;

end

r1:

sda <= 1'bz;

r2:

begin

led[7] <= sda;

sda <= 1'bz;

end

r3:

sda <= 1'bz;

r4:

begin

led[6] <= sda;

sda <= 1'bz;

end

r5:

sda <= 1'bz;

r6:

begin

led[5] <= sda;

sda <= 1'bz;

end

r7:

sda <= 1'bz;

r8:

begin

led[4] <= sda;

sda <= 1'bz;

end

r9:

sda <= 1'bz;

r10:

begin

led[3] <= sda;

sda <= 1'bz;

end

r11:

sda <= 1'bz;

r12:

begin

led[2] <= sda;

sda <= 1'bz;

end

r13:

sda <= 1'bz;

r14:

begin

led[1] <= sda;

sda <= 1'bz;

end

r15:

sda <= 1'bz;

r16:

begin

led[0] <= sda;

sda <= 1'bz;

end

ack9:

sda <= 0;

ack10:

sda <= 0;

stop3:

sda <= 0;

stop4:

sda <= 1;

default:

sda <= 1;

endcase

end

endmodule

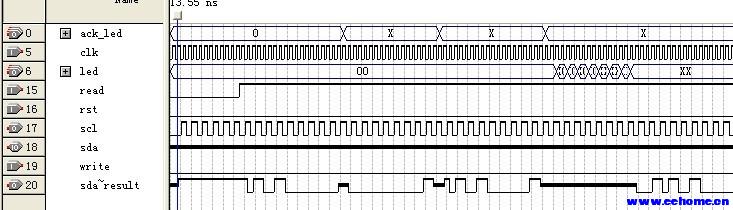

如何看这些波形

|

|

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图