本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

164 为 8 位移位寄存器,其主要电特性的典型值如下:

54/74164185mW 54/74LS164 80mW

当清除端(CLEAR)为低电平时,输出端(QA-QH)均为低电平。 串行数据输入端(A,B)可控制数据。当 A、B任意一个为 低电平,则禁止新数据输入,在时钟端(CLOCK)脉冲上升沿作用下Q0 为低电平。当A、B 有一个为高电平,则另一个就允许输入数据,并在CLOCK 上升沿作用下决定Q0 的状态。

引脚功能:

CLOCK :时钟输入端

CLEAR: 同步清除输入端(低电平有效)

A,B :串行数据输入端

QA-QH: 输出端

图1 74LS164封装图

图2 74LS164 内部逻辑图

极限值

电源电压7V

输入电压……… 5.5V

工作环境温度

54164………… -55~125℃

74164………… -0~70℃

储存温度……-65℃~150℃

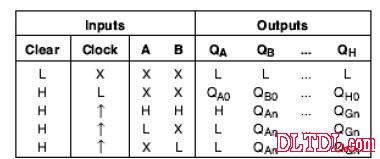

图3 真值表

H-高电平 L-低电平 X-任意电平

↑-低到高电平跳变

QA0,QB0,QH0 -规定的稳态条件建立前的电平

QAn,QGn -时钟最近的↑前的电平

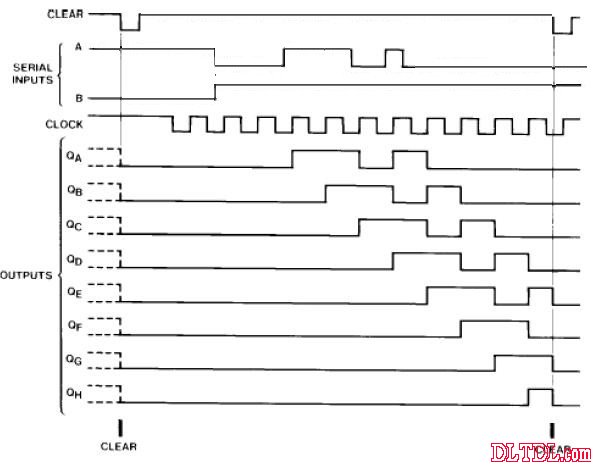

图4 时序图

建议操作条件

符号 参数最小值 典型值最大值单位 VCC 电源电压4.75 5 5.25 V VIH 输入高电平电压ViH 2 --V VIL 输入低电平电压ViL --0.8 V IOH 输出高电平电流IOH---0.4 mA IOL 输出低电平电流IOL --8 mA fCLK 时钟频率fCP 0 -25 MHz tW 脉冲宽度时钟20 --ns 清除 20 --tSU 数据设置时间17 --ns tH 数据保持时间5 --ns tREL 建立时间 30 --ns TA 工作温度0 -70 ℃

电气特性

符号参数 测试条件最小值典型值 最大值单位 VI 输入钳位电压VCC = Min, II = -18 mA ---1.5 V VOH 输出高电平电压 VCC = Min, IOH = Max VIL = Max, VIH = Min 2.7 3.4 -V VOL 输出低电平电压 VCC = Min, IOL = Max VIL = Max, VIH = Min -0.35 0.5 V IOL = 4 mA, VCC = Min -0.25 0.4 II 最大输入电压时输入电流 VCC = Max, VI = 7V --0.1 mA IIH 输入高电平电流 VCC = Max, VI = 2.7V --20 μA IIL 输入低电平电流 VCC = Max, VI = 0.4V ---0.4 mA IOS 输出短路电流VCC = Max (Note 4) -20 --100 mA ICC 电源电流VCC = Max (Note 5) -16 27 mA

动态特性(TA=25℃)

符号 参数 To (Output) RL = 2kΩ单位 CL = 15 pF CL = 50 pF 最小值 最大值最小值 最大值 fMAX 最大时钟频率 -25 - - - MHz tPLH 低到高电平输出传递延迟时间 时钟输出 - 27 - 30 ns tPHL 高到低电平输出传递延迟时间 时钟输出 - 32 - 40 ns tPHL 传递延迟时间 时钟输出 - 36 - 45 ns |

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图