本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

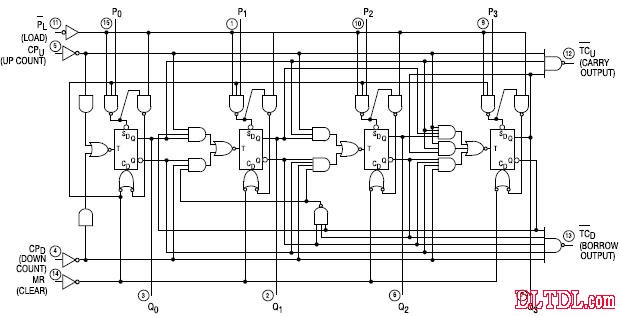

74LS192同步可逆递增/递减BCD 计数器

74LS193同步可逆递增/递减四位二进制计数器

特点:电路可进行反馈,而很容易的被级联。即把借位输出端和进位输出端分别反馈到后级计数器的减计数输入端和加计数输入端上即可。

·芯片内部有级联电路

·同步操作

·每触发器有单独的预置端

·完全独立的清零输入端

真值表: MRPLCPUCPDMODE工作模式HXXXReset (Asyn.)清除LLXXPreset (Asyn.)预置LHHHNo Change保持LH↑HCount Up加计数LHH↑Count DowN 减计数

H=高电平 L=低电平 X=不定(高或低电平) ↑=由“低”→“高”电平的跃变

引脚功能表:CPUCount Up Clock Pulse Input 计数芯片时钟脉冲输入 CPD Count Down Clock Pulse Input 倒计时时钟脉冲输入 MRAsynchronous Master Reset (Clear) Input 异步主复位(清除)输入 PL Asynchronous Parallel Load (Active LOW) Input 异步并行负载(低电平)输入 Pn Parallel Data Inputs 并行数据输入 Qn Flip-Flop Outputs (Note b) 触发器输出(附注b ) TCD Terminal Count Down (Borrow) Output (Note b) 终端倒计时(借)输出(注b ) TCUTerminal Count Up (Carry) Output (Note b) 终端数最多输出

图1 74LS192 逻辑图

图2 74LS193 逻辑图

图2 74LS193 逻辑图

图3 74LS192/74LS193引脚图

图4 逻辑符号

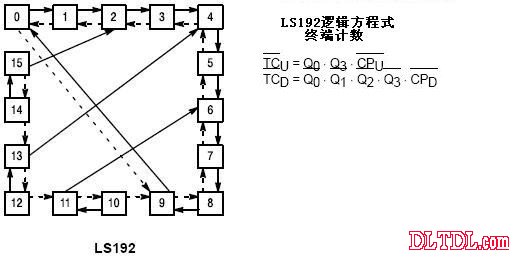

图5 74LS192 状态图

图6 74LS192 状态图

Operating Conditions 建议操作条件: Symbol 符号Parameter 参数 最小典型最大UNIT 单位VCCSupply Voltage 电源电压54 4.5 5.0 5.5 V744.755.05.25TAOperating Ambient Temperature Range操作环境温度范围54 –5525 125 ℃7402570IOHOutput Current — High 输出电流-高电平54,74--–0.4mAIOLOutput Current — Low 输出电流-低电平54 --4.0 mA74--8.0

DC SPECIFICATIONS直流电气规格: Symbol 符号Parameter 参数Limits限制范围UNIT 单位Test Conditions 条件最小典型最大VIHInput HIGH Voltage输入高电平电压2.0--VGuaranteed Input HIGH Voltage for All InputsVILInput LOW Voltage 输入低电平电压54--0.7vGuaranteed Input LOW Voltage for All Inputs74--0.8VIKInput Clamp Diode Voltage 钳位二极管输入电压-–0.65-1.5VVCC = 最小, IIN = –18 mAVOHOutput HIGH Voltage 输出高电平电压542.53.5-VVCC = 最小, IOH = 最大, VIN = VIH CC OH IN IH or VIL per Truth Table真值表742.73.5-VOLOutput LOW Voltage 输出低电平电压 54,74-0.250.4vIOL=4.0mAVCC = VCC 最小, VIN = VIL or VIH VIN = VIL or VIH per Truth Table74-0.350.5IOL=8.0mAIIHInput HIGH Current输入高电平电流--20μAVCC = 最大, VIN = 2.7 V--0.1mAVCC = 最大, VIN = 7.0 VIILInput LOW Current输入低电平电流 --–0.4mAVCC = 最大, VIN = 0.4 VIOSShort Circuit Current (Note 1)短路电流–20-–100mAVCC = 最大ICCPower Supply Current电源电流--34mAVCC = 最大

AC CHARACTERISTICS (TA = 25℃) 交流特性(TA = 25℃): Symbol 符号Parameter 参数Limits限制范围UNIT单位Test Conditions 测试条件最小典型最大fMaxMaximum Clock Frequency最大时钟频率2532-MHzVCC=5.0V CL=15pFtPLH tPHLCPU Input to TCU Output CPU输入到TCU输出-17 1826 24nstPLH tPHLCPD Input to TCD Output CPD输入到TCD输出-16 1524 24nstPLH tPHLClock 到 Q-27 3038 47nstPLH tPHLPL 到 Q-24 2540 40nstPHLMR Input to Any Output-2335ns

交流安装要求(TA = 25℃) Symbol 符号Parameter 参数Limits 限制范围 UNIT 单位

Test Conditions 测试条件 最小典型最大tW Any Pulse Width 任何脉冲宽度20 --ns VCC = 5.0Vts Data Setup Time 数据设置时间20 --ns th Data Hold Time 数据保持时间5.0 --nstrec Recovery Time 恢复时间40 --ns

图7 交流波形

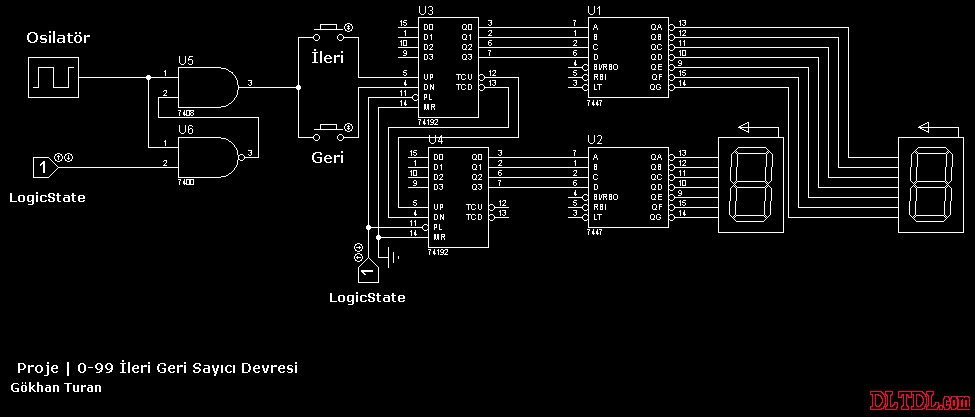

应用电路图:

图8

图9

原理:本电路复杂程度为55个等效门。本电路通过同时触发所有触发器而提供同步操作,以便在使用控制逻辑结构时,输出端的变化可相互重合。四个主从触发器的输出端,由两计数(时钟)输入之一的“低”到“高”电平的过渡而被触发。计数方向在其它计数输入端为“高”时,由脉冲的计数输入端所定。输出将符合独立于计数脉冲的数据输入的改变。该特点可使电路以预置输入而简单地更改计数长度,用作N 模数分频器(除法器)。清零输入在加高电平时,迫使所有输出端为低电平。清零功能独立于计数输入和置数输入。清零、计数和置数等输入端都是缓冲过的,它降低了驱动的要求,这就可减少为长字所要求的时钟驱动器数等等。本电路都设计成可被直接级联而勿需外接电路。借位和进位两输出端可级 联递增计数和递减计数两功能。借位输出在计数器下谥时,产生宽度等于递减计数输入的脉冲;同样,进位输出在计数器上谥时, 产生宽度等于递加计数输入的脉冲。因而 |

|

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图