本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

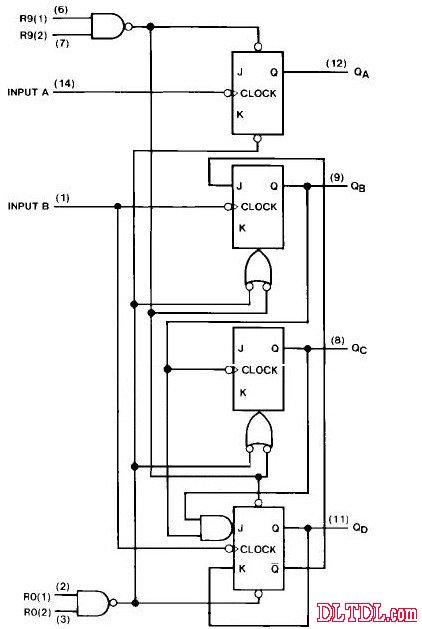

74LS90功能:十进制计数器(÷2 和÷5)

原理说明:本电路是由4 个主从触发器和用作除2 计数器及计数周期长度为除5 的3 位2 进制计数器所用的附加选通所组成。有选通的零复位和置9 输入。

为了利用本计数器的最大计数长度(十进制),可将B 输入同QA 输出连接,输入计数脉冲可加到输入A 上,此时输出就如相应的功能表上所要求的那样。

LS90 可以获得对称的十分频计数,办法是将QD 输出接到A 输入端,并把输入计数脉冲加到B 输入端,在QA 输出端处产生对称的十分频方波。

真值表:Reset Inputs复位输入 输出 R0(1) R0(2) R9(1) R9(2) QD QC QB QA H H L X L L L L H H X L L L L L X X H H H LLH X L X L

COUNT

COUNT

COUNT

COUNT L X L X L X X L X L L X

H=高电平 L=低电平 ×=不定

BCD 计数顺序(注1)Count

输出 QD QC QB QA 0 L L L L 1 L L L H 2 L L H L 3 L L H H 4 L H L L 5 L H L H 6 L H H L 7 L H H H 8 H L L L 9 H L L H

5-2 进制计数顺序(注2)Count

输出 QA QD QC QB 0 L L L L 1 L L L H 2 L L H L 3 L L H H 4 L H L L 5 H L L L 6 H L L H 7 H L H L 8 H L H H 9 H H L L

注1:对于BCD(十进)计数,输出QA 连到输入B 计数

注2:对于5-2 进制计数,输出QD 连到输入A 计数

图1 74LS90引脚图

图2 74LS90逻辑图

Recommended Operating Conditions建议操作条件:Symbol 符号Parameter 参数最小典型最大UNIT 单位VCCSupply Voltage 电源电压4.7555.25VVIHHigh Level Input Voltage输入高电平电压2--VVILLOW Level Input Voltage 输入低电平电压--0.8VIOHHIGH Level Output Current高电平输出电流---0.4mAIOLLOW Level Output Current低电平输出电流--8mAfCLKClock Frequency (Note 5)时钟频率A to QA0-32MHzB to QB0-16fCLKClock Frequency (Note 6)时钟频率A to QA0-20MHzB to QB0-10tWPulse Width (Note 5)脉冲宽度A15--nsB30--Reset15--tWPulse Width (Note 6)脉冲宽度A25--nsB50--Reset25--tRELReset Release Time (Note 5)重置发布时间25--nstRELReset Release Time (Note 6)重置发布时间35--nsTAFree Air Operating Temperature工作温度0-70℃Note 5: CL = 15 pF, RL = 2 kW, TA = 25℃ and VCC = 5VNote 6: CL = 50 pF, RL = 2 kW, TA = 25℃ and VCC = 5V

Electrical Characteristics 电气特性over recommended operating free air temperature range (unless otherwise noted)Symbol 符号Parameter 参数Conditions 条件最小典型最大UNIT 单位VIInput Clamp Voltage输入钳位电压VCC = 最小, II = -18mA---1.5VVOHHIGH Level Output Voltage输出高电平电压VCC=最小,IOH=最大 VIL=最大,VIH=最小2.73.4-VVOLLOW LevelOutput Voltage输出低电平电压VCC = 最小, IOL = 最大 VIL = 最大, VIH = 最小(Note 8)-0.350.5VIOL= 4mA, VCC =最小-0.250.4IIInput Current @ MAX Input Voltage输入电流@最大输入电压VCC = 最大, VI =7VReset--0.1mAVCC = 最大 VI =5.5VA--0.2B--0.4IIHHIGH Level Input Current输入高电平电流VCC = 最大, VI =2.7VReset--20μAA--40B--80IILLOW LevelInput Current输入低电平电流VCC = 最大, VI =0.4VReset---0.4mAA---2.4B---3.2IOSShort Circuit Output Current短路输出电流VCC = 最大 (Note 9)-20--100mAICCSupply Current电源电流VCC = 最大 (Note 7)-915mA

交流电气特性:Symbol 符号Parameter 参数To (Output)RL=2KUNIT 单位CL =15pFCL =50pF最小最大最小最大fMaxMaximum Clock Frequency最大时钟频率A to QA32-20-MHzB to QB16-10-tPLHPropagation Delay Time LOW-to-HIGH Level Output低到高电平输出传递延迟时间A to QA-16-20nstPHLPropagation Delay Time HIGH-to-LOW Level Output高到低电平输出传递延迟时间A to QA-18-24nstPLHPropagation Delay Time LOW-to-HIGH Level Output低到高电平输出传递延迟时间A to QD-48-52nstPHLPropagation Delay Time HIGH-to-LOW Level Output高到低电平输出传递延迟时间A to QD-50-60nstPLHPropagation Delay Time LOW-to-HIGH Level Output低到高电平输出传递延迟时间B to QB-16-23nstPHLPropagation Delay Time HIGH-to-LOW Level Output高到低电平输出传递延迟时间B to QB-21-30nstPLHPropagation Delay Time LOW-to-HIGH Level Output低到高电平输出传递延迟时间 |

|

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图