本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

混合集成特定频率信号发生器的设计

混合集成特定频率信号发生器主要应用于某军用引信安全控制系统。它在该引信设计中起着中枢神经的作用,主要用于实现全电子安全系统状态的控制,即按预定条件(如时间、气压、指令等)控制引信在一定逻辑程序作用下,正确实现保险设置、保险解除、环境信息综合判断、特定频率信号产生等控制功能。该系统可根据鱼雷的特点和使用要求来控制三级保险的设置。依靠敏感的系统发射或运动过程中不同的独立航道环境或指令来解除保险,以确保系统使用过程中的安全,同时选用简单、成熟的保险机构来提高可靠性。

混合集成特定频率信号发生器的设计主要是采用可编程逻辑器件进行逻辑编程,以实现高性能系统所需求的复杂逻辑功能。该方法可大大减小元器件数量,增加系统可靠性,而且工作状态稳定,反应速度快,设计周期短,系统成本低。其工艺采用先进的厚膜混合集成技术,产品重量轻,体积小,可靠性高,一致性好。

1 电路设计原理框图

该电路的基本原理框图如图1所示。它主要由晶体振荡器为两个可编程逻辑器件(isp1016E)提供4.096MHz的频率信号,并经分频产生1 kHz信号,然后将其作为计数器的时钟触发。三级开关信号(即系统中的解保信号)依次加到四光电耦合器上,其中第一级开关信号用于驱动可编程逻辑器件isp1016E-1,其输出信号经过驱动器转换后,可将原来输出端的高电平信号转换为低电平信号,以解除系统第一级保险。

第二级开关信号经光耦隔离后用于驱动另一个可编程逻辑器件isp1016E-2,该信号经判断确认时序正确时,isp1016E-2的输出信号经驱动器可产生低电平信号,以解除系统第二级保险。

当第三级开关信号到来并确认当前的三级开关信号时序关系正常后,系统便通过isp1016E-2产生特定频率和占空比的5 V TTL信号,以解除第三级保险,从而使系统进行高压充电,此时引信处于待爆状态。

当三级开关信号时序不正常时。第四路开关信号经过光耦隔离可为两只isp1016E提供复位信号,以使特定频率信号输出端无输出,从而使引信绝火。

2 方案设计

传统数字电路中多由TTL和CMOS器件构成逻辑电路,这样的系统大多存在逻辑器件数目多,电路复杂,板块庞大等缺点。而可编程逻辑器件内部有大量的门电路(2000门)和触发器,通过编程可以连接成各种中小规模的数字电路。这样。寄存器、计数器、多路选择、译码器等电路都很容易通过编程实现。另外,也可以利用可编程逻辑器件配套软件中具备的宏单元库,来编程完成高性能系统所要求的复杂逻辑功能。

由于混合集成特定频率信号发生器的逻辑关系比较复杂,为此,本设计选用可编程逻辑器件isp1016E来实现逻辑功能。以简化设计难度。这样,只要在计算机上输入数字电路原理图或用硬件描述语言描述数字电路,然后经过编译,并将编译后的数据文件下载到可编程逻辑器件上即可完成数字电路的设计,而且电路结构简单,器件少,成本低,设计方便,不容易损坏,同时可大大增加系统的可靠性、减少系统体积。

3 软件设计

混合集成特定频率信号发生器软件由isp1016E-1芯片软件和isp1016E-2芯片软件组成。用于实现有效环境信号的识别、时序判断、两级保险的解除、特定频率信号的产生等功能。设计时应首先定义可编程逻辑器件isp1016E的I/O端口,然后采用Viewlogic软件对系统可编程逻辑器件进行仿真设计。设计编译完成后,便可将数据文件下载到可编程器件中。IspLSI器件可在线路板上编程;也可在专用编程器上编程。

3.1 isp1016E-1芯片设计

isp 1016E-1芯片主要用来实现有效环境信号识别、第一级保险的解除等功能。其设计思想首先是将外接晶振频率分频至1 kHz,以将其作为计数器的时钟触发,每毫秒采样一次第一级开关信号(即解保信号)来对有效信号进行计数,当计数至第N次时,截止计数过程并发驱动信号,接着输出低电平以驱动后序第一级保险动作,同时将信号传至isp 1016E-2。

3.2 isp1016E-2芯片设计

isp 1016E-2芯片用于完成第二、第三级保险解除控制逻辑、时序判断、特定频率信号的产生等功能。可采用同样的分频与累计计数方法,来对二、三级解保信号进行抗干扰滤波处理。若接收到第二级解保信号且判断一、二级解保信号时序正确,则发驱动信号并变为低电平,同时驱动第二级保险动作;若判断时序不对,则封闭第二级解保信号接收通路(不再接收);在接收到控制系统给出的第三级解保信号并确认这三级解保信号的时序关系正常后,系统将输出特定频率和占空比的5 V特定频率信号。

4 系统可靠性及版图设计

为了使电路能更安全可靠的工作,各路的开关信号都先经过光耦再输入电路。输人地与输出地严格分开可保证电路电子元器件的安全;为了减小外界对电源的干扰,设计时应在供电电源与地之间、芯片的工作电源上都接入滤波电容以进行滤波处理,从而保证电路正常工作。

电路程序设计包含了对各种环境信息的综合判断,如抗干扰、抗抖动处理、时序判断等功能。采用“时间窗、时序判断”等技术措施进行综合控制设计可滤除ms级的干扰信号,从而保证系统安全可靠地工作。

此外,该电路还具有单检与重新解保功能。程控采用双套备份、冗余设计。需要单套检验与联试时,可以给一套程控的isp芯片一直加上复位信号,这样可检验另一套引信的功能;在系统运行过程中,如在三级解保后发现目标跟踪有误,可以接收复位信号,并通过程控重新进行解保动作。

在版图设计时,器件的放置和分布既要考虑电路合理布局,散热均匀,也应考虑工艺加工过程中的组装生产。具体可将元件按照功能相对集中放置;输入、输出线分开放置,并按工作顺序排列;布线时,电源线和地线均应短而粗,要尽量减少相互之间的电磁干扰。

该电路共采用两片逻辑器件来完成逻辑功能。每一片芯片有44只管脚(PLCC封装)。两片芯片之间、芯片与外围电路之间都会相互提供信号,连线纵横交错,交叉往来连线复杂,且电路体积要求也比较严格,这都会在版图设计过程中增加布版的难度。因此,在设计时,两只芯片的放置位置与方向要用画图软件反复比较和验证,以尽量减少相互之间走线的交错和复杂度;布线时最好将纵线在同一层面,横线在另一层面,并用介质绝缘。在线路走线上,连线应尽可能短,并使布线尽可能优化。

5 工艺制作及加工

本产品的工艺加工没有选用PCB板表面贴装技术,主要是因为PCB板组装时过多的焊接连线、焊点、接插件等严重阻碍了生产率和可靠性的进一步提高;另外,电路的工作频率和速度的提高也要求尽量缩短信号在系统内的传输延迟。为此,电路专门选用了厚膜混合集成工艺,即用厚膜多层布线工艺来制作导电带和电阻器;晶体管、单片集成电路等则采用裸芯片组装金丝球焊键合,封口采用平行缝焊技术充氮气密封。厚膜工艺可减少电路体积,提高精度、稳定性和产品可靠性,且利于批量生产。

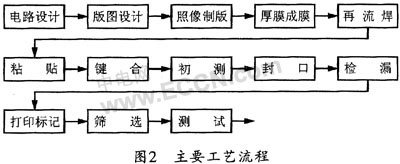

在厚膜工艺中,电容器应采用粘接工艺;光藕、MOS管等器件应采用载流焊工艺。PLCC封装的可编程逻辑器件加工相对比较少。在初期载流焊组装逻辑器件过程中,由于逻辑器件管脚较多且细短(焊区面积仅1.8mm×0.4mm,相邻管脚的间距约0.3mm),故在点焊料时,因焊料流量不容易控制,焊料极易将相邻管脚粘连在一起而造成短路现象。加工时经常要擦除短路处的焊料并重新点胶反复操作,这都会极大地影响效率。经过摸索实验。笔者专门配置了直径较小的点焊剂的针孔来减小流量和焊接面积,图2给出了该产品的主要工艺流程图。

6 结束语

混合集成特定频率信号发生器是某军事系统中常用的组件之一。本文通过在软件、制版、工艺等方面的一系列设计,最终实现了该器件逻辑功能的集成化、小型化。经多次联机测试证明,该器件性能稳定、工作正常、其电性能指标完全满足系统和用户的要求。目前,用户已连续小批量订货。此外,该产品还可以根据系统需要修改程序软件,以输出不同频率、不同占空比的信号。由此可见,该产品具有易于扩展和设计升级等优点。而且电路体积小、精度高、重量轻,使用灵活,具有重要的使用价值和良好的应用前景。 |

|

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图