本文包含原理图、PCB、源代码、封装库、中英文PDF等资源

您需要 登录 才可以下载或查看,没有账号?注册会员

×

1.引言

在移动通信和高速无线数据通信中,多径效应和信道带宽的有限性以及信道特性的不完善性导致数据传输时不可避免的产生码间干扰,成为影响通信质量的主要因素,而信道的均衡技术可以消除码间干扰和噪声,并减少误码率。其中判决反馈均衡器(DFE)是一种非常有效且应用广泛得对付多径干扰得措施。目前DFE大致有以下几种实现方法:1)采用多片通用数字滤波器集成电路级联方式,但同时由与多片带来的体积和功耗的增加,在实际中运用不多。2)采用DSP来实现,如MotorolaSC140就是单片的可编程均衡器,采用软件来实现算法,但由于受器件功能限制,在实时性要求极高的场合中受到限制。3)采用可编程逻辑器件实现,随着可编程逻辑器件逻辑门数量和速度的不断增加,在单片上实现系统集成已经成为可能,而且FPGA特别适合实现可配置的判决反馈均衡器。

2.判决反馈均衡器的基本原理

判决反馈均衡器(DFE)是一种非线性均衡器。如图1所示,由前馈部分(由FIR滤波器组成)和反馈部分(由IIR滤波器组成)组成,前馈部分可以抵消在时间上超前的码间干扰和在时间是滞后的码间干扰(由中心抽头的位置决定),反馈部分可以抵消在时间上滞后的码间干扰。

均衡器的输出为:

式中M,N分别为前馈滤波器和反馈滤波器的长度。抽头系数更新采用DD_LMS(directdecisionleastmeansquare)和CMA(constantmodulusalgorithm)算法,CMA是一种盲自适应算法,即不需要训练序列,可以让均衡器收敛到较低的MSE水平,但由于CMA的误差量较大,从而步长较小,CMA的跟踪能力有限,因而,在DFE设计中,CMA常常作为均衡器的初始化算法,即对多径信号的时延和幅度进行粗略估计。而DD_LMS算法相对于CMA有更低的MSE水平,并且DD_LMS具有较低的误差量,从而步长更大,跟踪能力强,因而,在DFE设计中,DD_LMS常常作为均衡器稳定后的自适应算法。

3.设计思想

由于我们设计的DFE是一个比较复杂的系统,我们在设计中根据功能块自下而上分层次进行,这样可以节省设计时间,减少设计输入的错误,消除重复的电路元件,并能简化校验于进行修改,在实际设计中,按照模块的大小和功能分成三部分:如图二所示,PARTI包括接口和DFE均衡器,PARTII包括判决器和误差控制函数运算模块,PARTIII为抽头系数调整部分。

出于灵活性的考虑,系统采用类似于集散控制而非集中控制的方案,也就是系统没有一个中心控制器,这样可以保持三个部分的相对独立,若要改变设计,比如改变算法,只需要改变误差控制函数运算模块即可。各模块的恰当分割大大增加了系统的灵活性。

4.各模块的FPGA实现

4.1接口模块

本系统并未涉及具体的A/D器件,仅根据常用的A/D器件的工作信号设计系统接口模块。

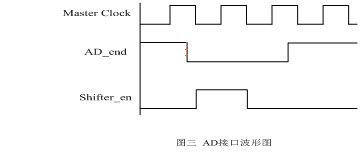

在转换完成后,一般A/D器件输出一个低电平信号作为A/D的允许信号。该信号在系统中为输入信号ad_end,接口模块系统时钟始终监控ad_end的电平变化,当检测到ad_end的低电平时,接口模块产生一个“开始”脉冲作为允许信号,允许DFE的延迟环节接收输入数据,并开始移位。其实现如图三所示。

4.2DFE模块

均衡器分为FFE(FeedforwardEqualizer)和FBE(FeedBackwardEqualizer)两部分,结构类似,前馈滤波器为32阶的FIR滤波器,反馈滤波器为64阶的IIR滤波器,滤波器系数宽度都为16位,精度为15位,输入数据宽度为12位,精度为10位,判决器输出数据为2位,精度为0位,该模块主要由输入移位寄存器和卷积模块组成。

(1)输入移位寄存器

对于前馈滤波器,由于共有32阶,因此输入寄存器的长度为32。定义一个32×12的二维数组FFF[32][12],复位信号有效时,FFF清零。复位信号无效,而输入使能信号有效时,每来一个时钟上升沿,就从输入端进入一个数据,上一时刻的数据分别前移一位,最前面的数据被第二个数据覆盖。

对于反馈滤波器,由于有64阶,因此输入寄存器的长度为64,定义一个64×12的二维数组FFF[64][12],数据输入方式和前馈滤波器相同。

(2)卷积部分的实现

对于前馈滤波器,输入数据宽度是12位,精度为10位,滤波器系数宽度为16位,精度为15位,输入数据为带符号数,数据的高位为符号位,为实现相乘运算,设计12×16位的乘法器,分别从前馈输入移位寄存器和前馈系数移位寄存器中取出数据和系数作为12×16的输入,这样32个乘法器就分别得到32个乘积,乘积的宽度为11+15,精度为10和15的数据相乘后得到的数据精度为25位,因此结果的小数点在第25位和26位之间。为减少系统的硬件开销,把乘法器的输出结果进行合理的截取,取精度为15位,低10位丢弃,这样乘法器的输出就变为从第11位到第27位的数据,宽度为17位,精度为15位。反馈滤波器实现与之类似。

4.3误差控制函数运算模块

误差控制函数运算模块主要完成判决输出以及误差控制函数的运算。不同的抽头更新算法在于误差控制函数的不同。判决器的功能是进行误差判决,判决器判决部分比较简单,由于二进制数采用补码表示,判决和误差的计算都可以用组合电路来实现。

4.4抽头系数调整模块

本模块完成抽头系数的自适应调整,模块主要由系数移位寄存器和系数调整运算模块组成。

(1)系数移位寄存器

对于前馈寄存器,相应的输入移位寄存器有32节,则系数移位寄存器也有32节。设置一个初始系数装入输出端,32个系数输入端,32个系数输出端,复位信号有效时,所有寄存器清零,初始系数串行装入,装入7个初始系数需要7个时钟周期,在装入使能有效时,每来一个时钟上升沿,装入一个系数,先装入的系数右移动一个寄存器,如果系数调整使能有效,则每来一个时钟上升沿就把来自系数调整运算模块调整后的系数并行装入到系数移位寄存器中。

对于反馈系数,移位寄存器有64节,移位原理同前馈滤波器。

(2)系数运算调整

抽头系数的调整可按上式来计算,其中为时刻前抽头系数向量,为时刻反馈抽头系数向量,为输入数据向量,为判决器输出向量,为误差控制函数计算模块的输出。

对于前馈抽头系数,输入的前一个时刻的系数来自前馈系数移位寄存器输出的系数,每来一个时钟,系数调整一次。为宽度12位,精度为10位的数据,为宽度为九位,精度为0位的数据,两者输入到一个12×9乘法器相乘后,得到宽度为11+8+1=20位,精度为10位的数据。由于在误差控制模块中计算时,只取了低9位,小数点右移了15位,现在把小数点左移15位得到宽度为26,精度为25的数据。截取高16位,得到宽度为16、精度为15的系数调整量。前一个时刻的系数和这个调整量输入到一个16位减法器,这里系数极小,所以不必考虑进位,得到一个宽度为16位、精度为15位的差,即调整后的系数,输出到前馈系数移位寄存器。

对于反馈抽头系数,输入的前一个时刻的系数来自反馈系数移位寄存器输出的系数。每来一个时钟,系数调整一次。为宽度为2、精度为0的数据,为宽度9位、精度0位的数据,两者输入到一个2×9乘法器相乘后,得到宽度为1+8+1=10位、精度为0位的乘积。同样把小数点左移15位,得到系数调整量。前一个时刻的系数和这个调整量输入到一个16位减法器,得到一个调整后的系数,宽度16位、精度15位。

4.5FPGA实现

整个设计全部用verilogHDL语言实现,FPGA芯片采用XC2VP70,采用SynplifyPro7.7进行综合,ncverilog5.0进行功能仿真,ISE6.3生成布线文件。根据综合结果对设计进行了优化,最后系统显示最高频率可到80M,上板测试功能正常,系统延迟控制在35us范围以内,可以满足绝大多数高速无线数据通讯系统对均衡器的要求。

5总结

本文作者创新点:针对高速无线数据通讯的实时性要求,提出采用FPGA来实现可配置均衡器的设计,在设计过程中采用自顶而下划分的设计方式,即方便了设计的需要,同时又满足了性能的要求,在实际项目中收到很好的效果。 |

|

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图

|手机版|MCU资讯论坛

( 京ICP备18035221号-2 )|网站地图